Part Number: XIO3130

Other Parts Discussed in Thread: XIO2001, , SN74AHC1GU04

Hello,

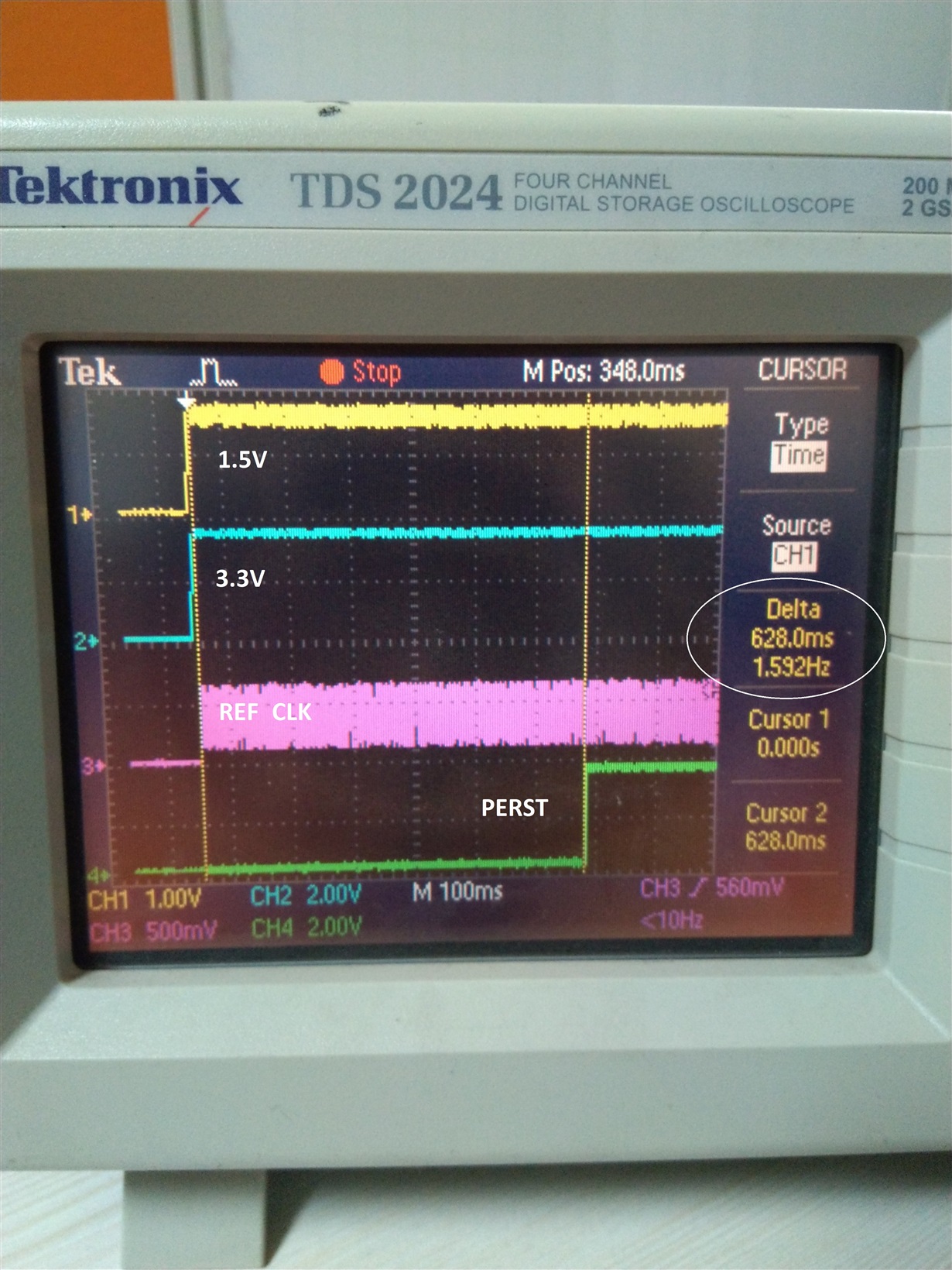

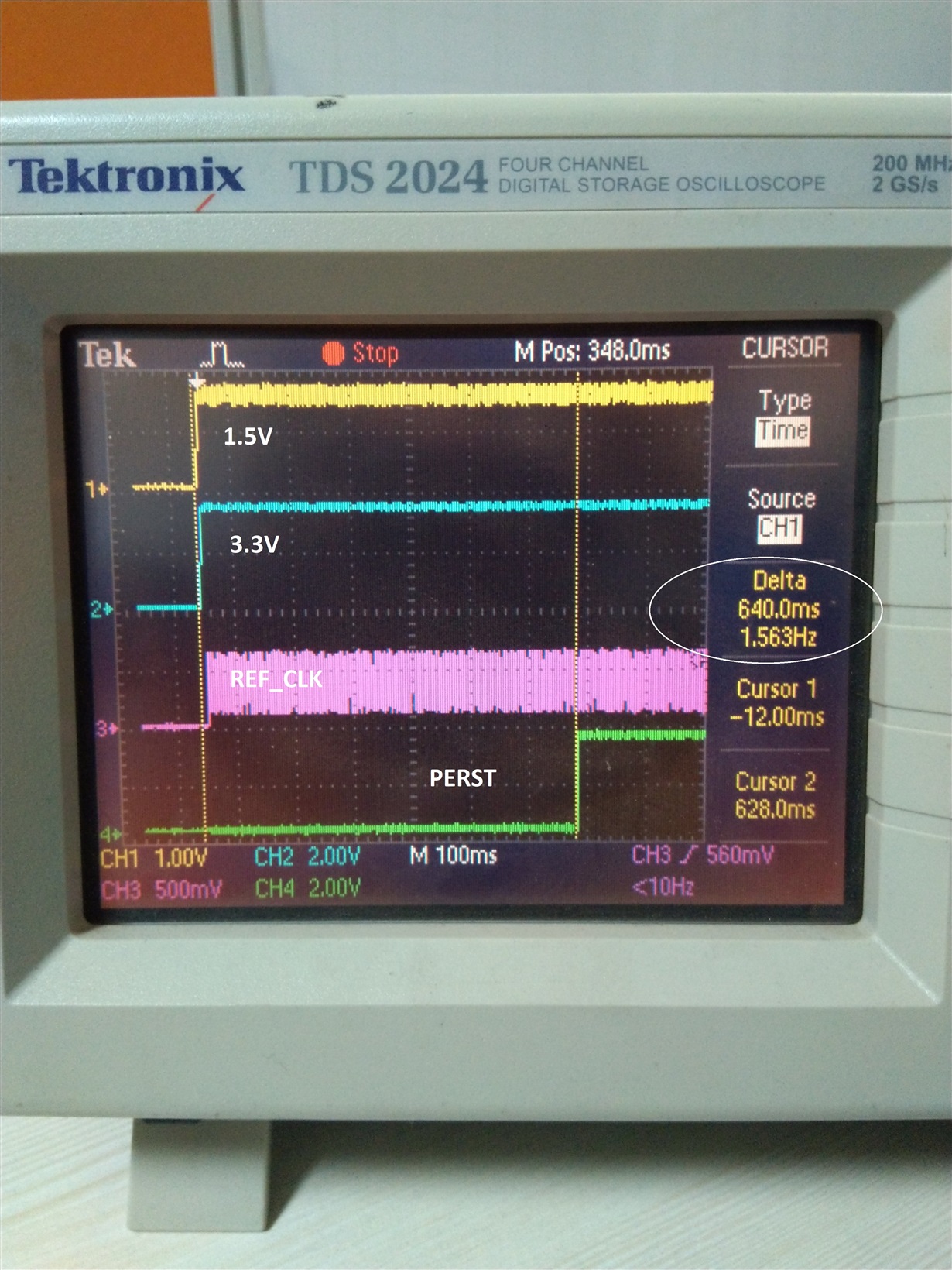

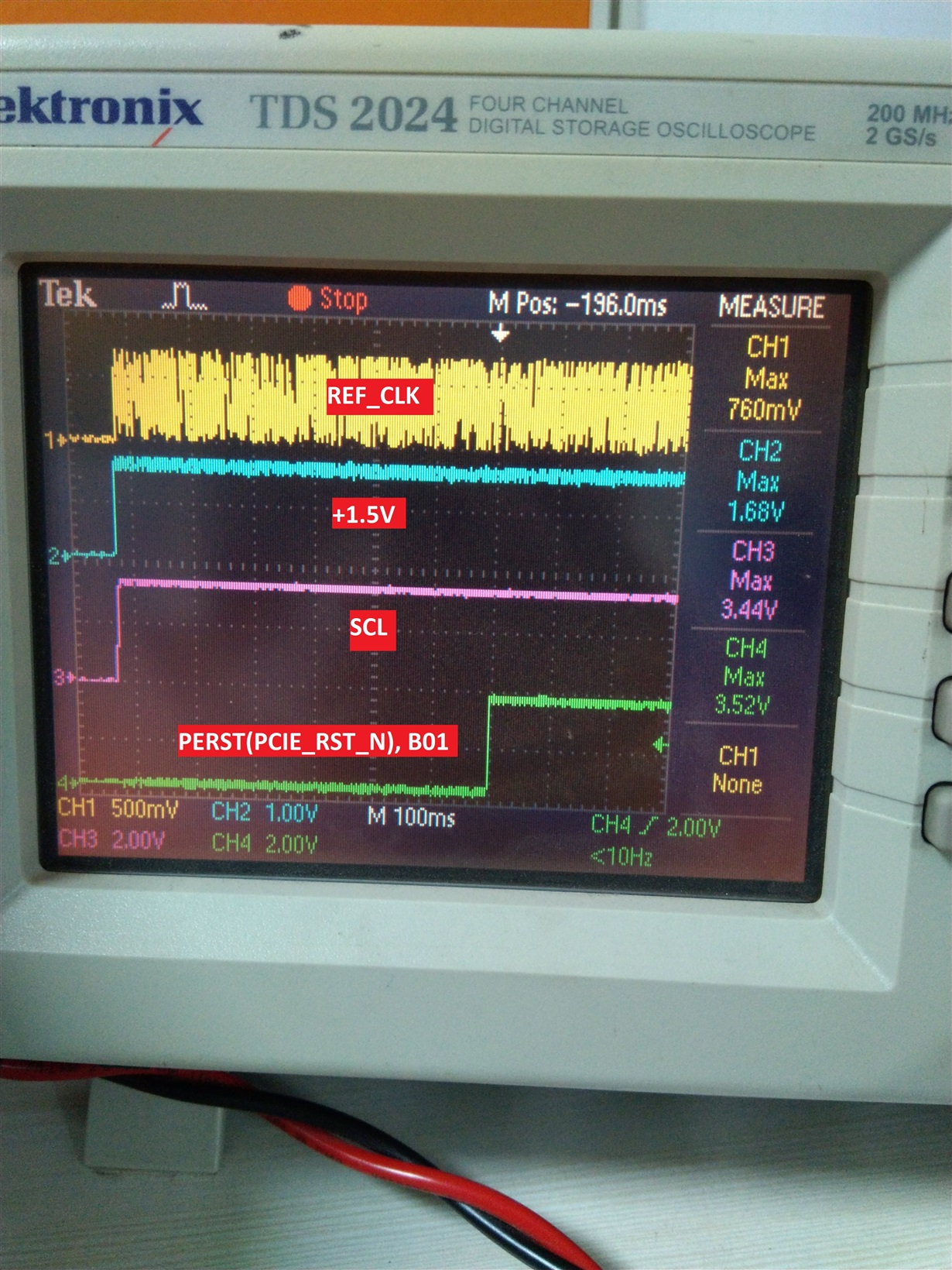

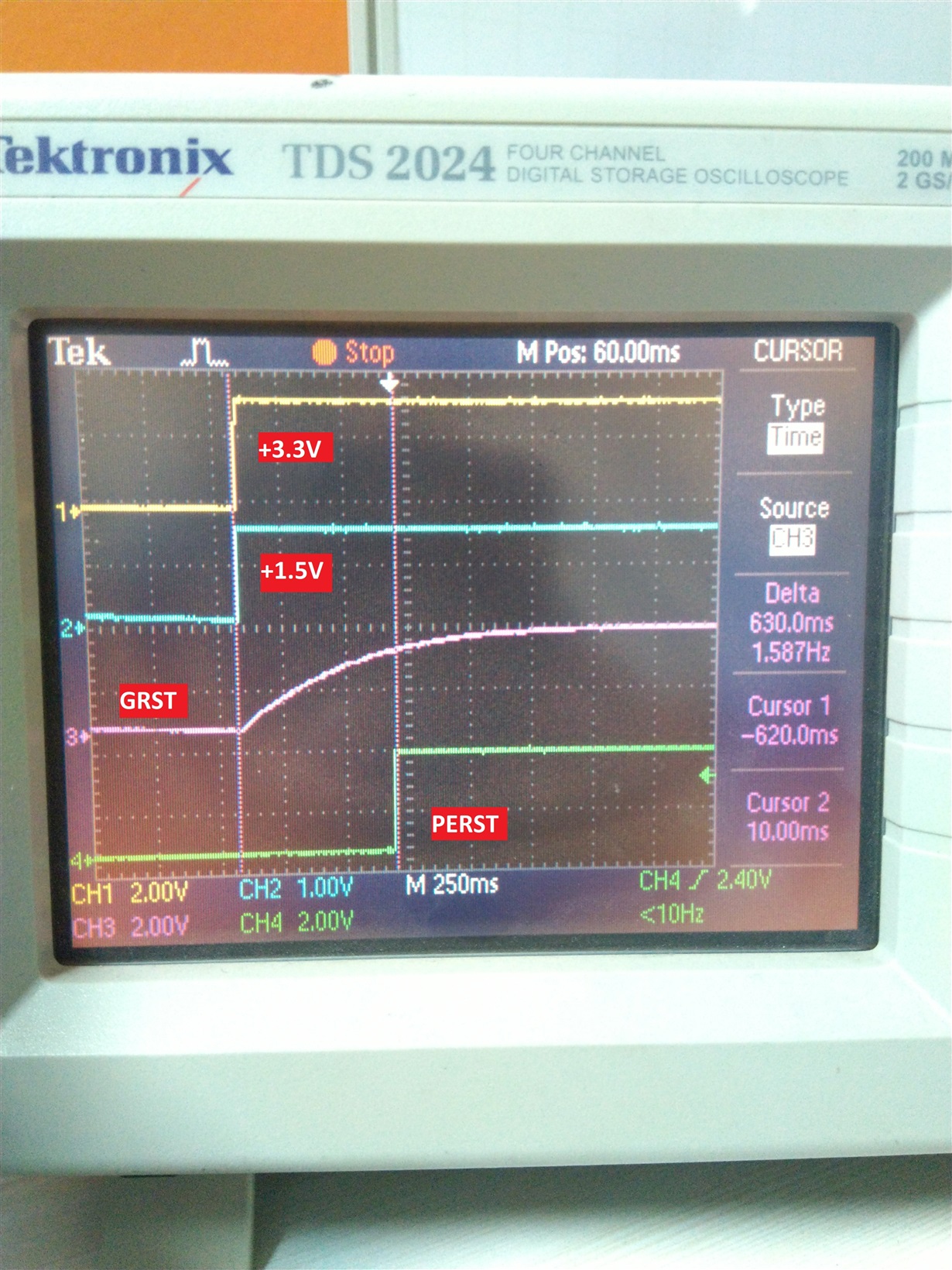

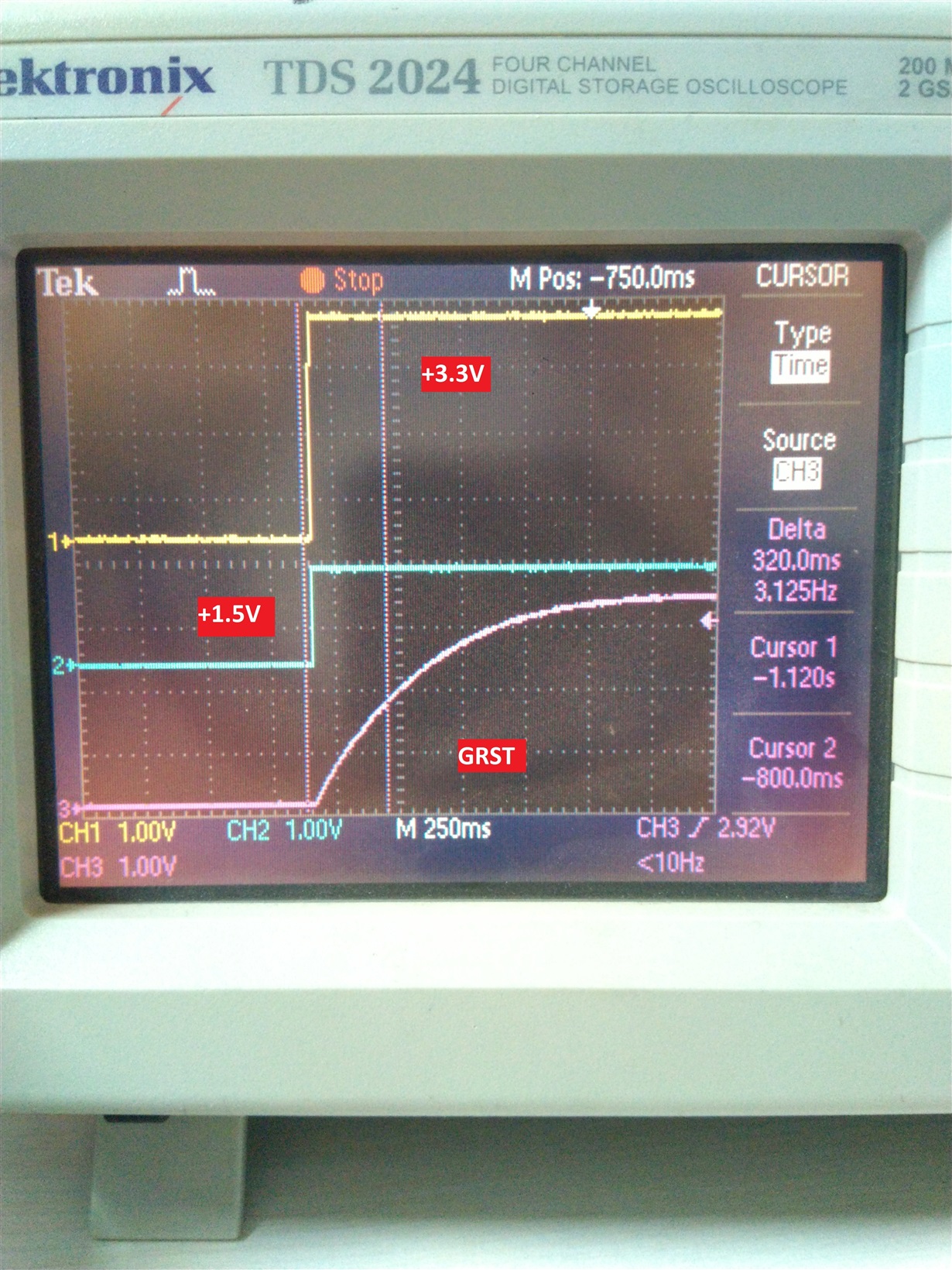

In our Design, We are using two XIO3130 PCIE Switch and connected the UP Stream Port to P1020’s SerDes1 & SerDes2 Port.

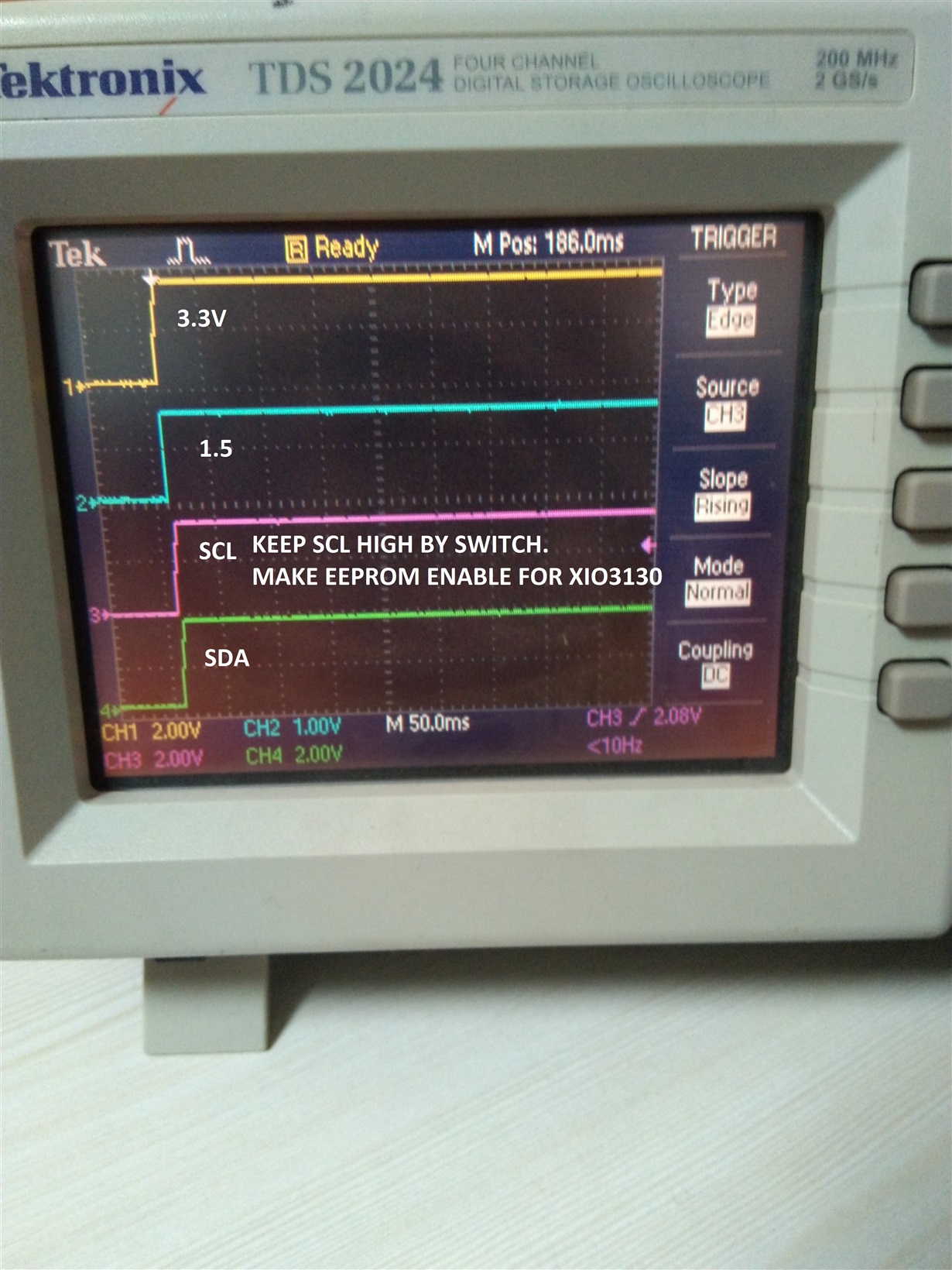

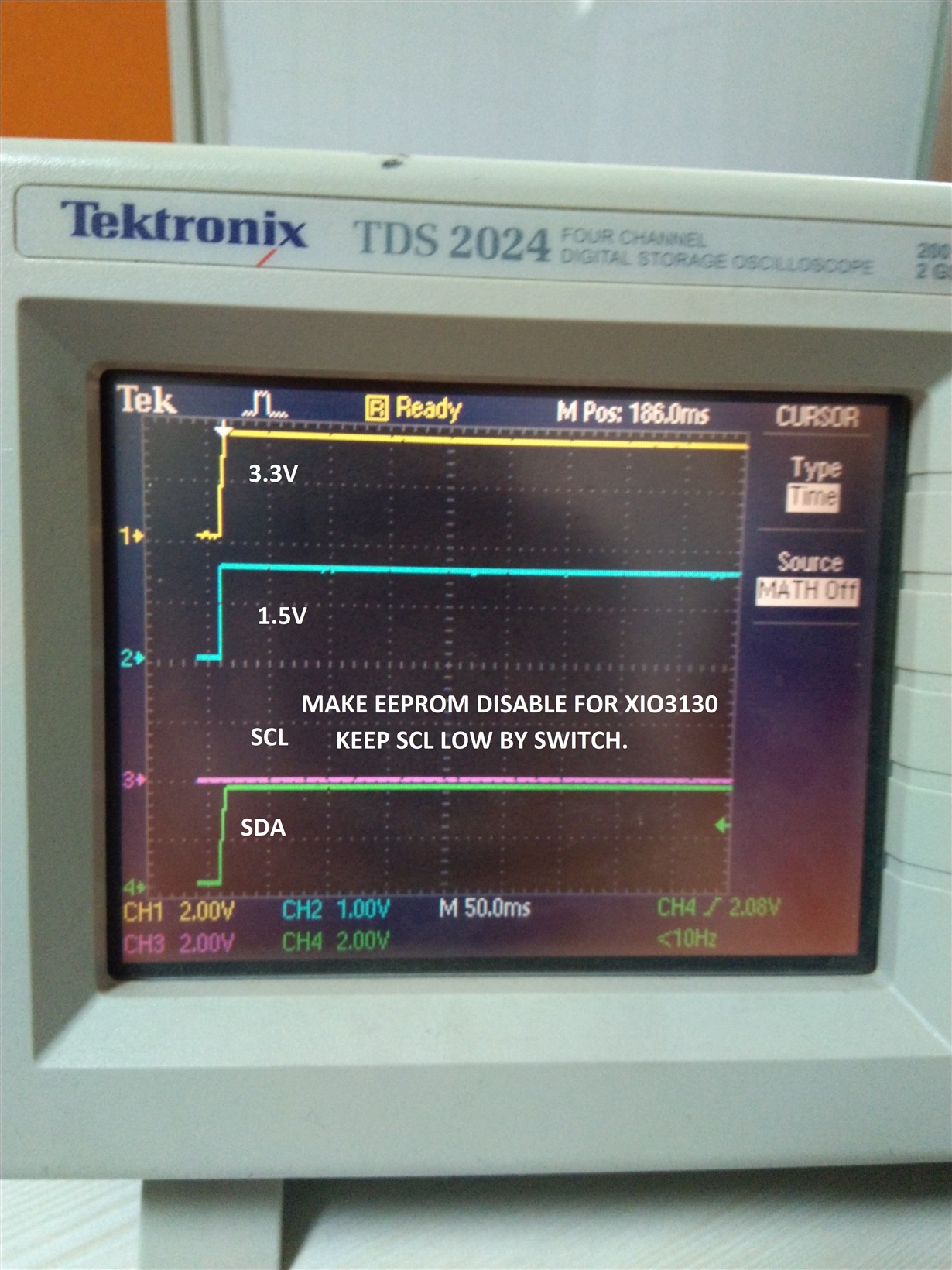

One EEPROM (AT24C04D-XHM-T) is connected with Each XIO3130 Switch through I2C.

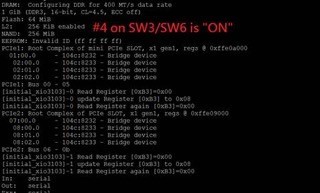

When we keep the SCL pin of I2C Low (SW3/SW4 -Pin#4 ON), we can see the all PCIE Switch in u-Boot but after keeping the SCL High(SW3/SW4 -Pin#4 OFF) the u-Boot can’t detect the PCIE Switch.

Here EEPROM is pre-programmed Externally as per TI Forum’s Guidance using Ardino.

We also share the Images for the u-Boot and EEPROM file for reference.

Regards,

Alpesh

4C 01000111 00 00000000 24 00100100 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 01 00000001 00 00000000 00 00000000 00 00000000 00 00000000 14 00010100 32 00110010 02 00000010 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 00 00000000 24 00100100 3F 00111111 04 00000100 01 00000001 00 00000000 01 00000001 00 00000000 00 00000000 00 00000000 00 00000000 14 00010100 32 00110010 10 00010000 60 01100000 1A 00011010 00 00000000 00 00000000 02 00000010 00 00000000 01 00000001 00 00000000 00 00000000 00 00000000 00 00000000 14 00010100 32 00110010 10 00010000 60 01100000 1A 00011010 00 00000000 00 00000000 02 00000010 00 00000000 01 00000001 00 00000000 00 00000000 00 00000000 00 00000000 14 00010100 32 00110010 10 00010000 60 01100000 1A 00011010 00 00000000 00 00000000