Hi Team,

We had been meet the TBT device lost when system do S4/S5 stress test, so we control HRESET assert when system on S4/S5 then can fixed as below waveform,

but, extend another issue is meet XHCI yellow ban when control HRESET assert on S4/S5.

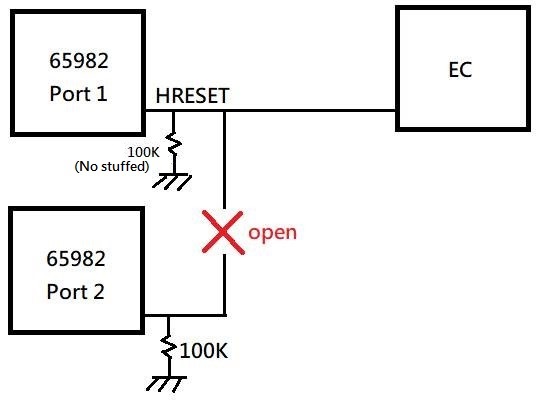

therefore, we separate HRESET between 65982 port 1 and port 2 with HW connection as below, them can fixed the XHCI yellow ban issue,

but side effect is 65982 port 2 will no function(load FW fail), could you please tell us how to control HRESET/MRESET/RESETZ timing from EC ?

?