Other Parts Discussed in Thread: DS90CF388

Hi team,

My customer want to use the SN65LVDS93A to serial the SPI signal from the FPGA.

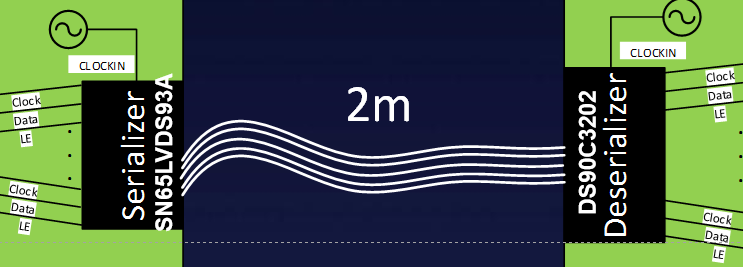

The application diagram is as below:

The data rate is about 100MHz, the SPI signal and the clock is from the FPGA GPIO.

The voltage level is CMOS3.3 and CMOS1.8 or LVDS

So several questions need your support:

1. Can the device support the transmit the SPI signal?

2. Can they use the FPGA GPIO to generate the Clock for the device? Is there any limit for the input clock?

3. They need 2m cable to transmit the data, can you help to recommend the type of the cable?

4. Please help to review if the DS90C302 can support the receiver application?

5. What's the latency different between 4 LVDS output?

Lacey

Thanks a lot!

Thanks a lot!