Part Number: DS90UB964-Q1

Tool/software: Linux

Hi,ti

I have some questions about the pattern generator.

I have read section 8.5.6.1 and used the example, I changed the first line of code to enable CSI1,WriteI2C(0x32,0x01)-->WriteI2C(0x32,0x12), but it displays the same as before.

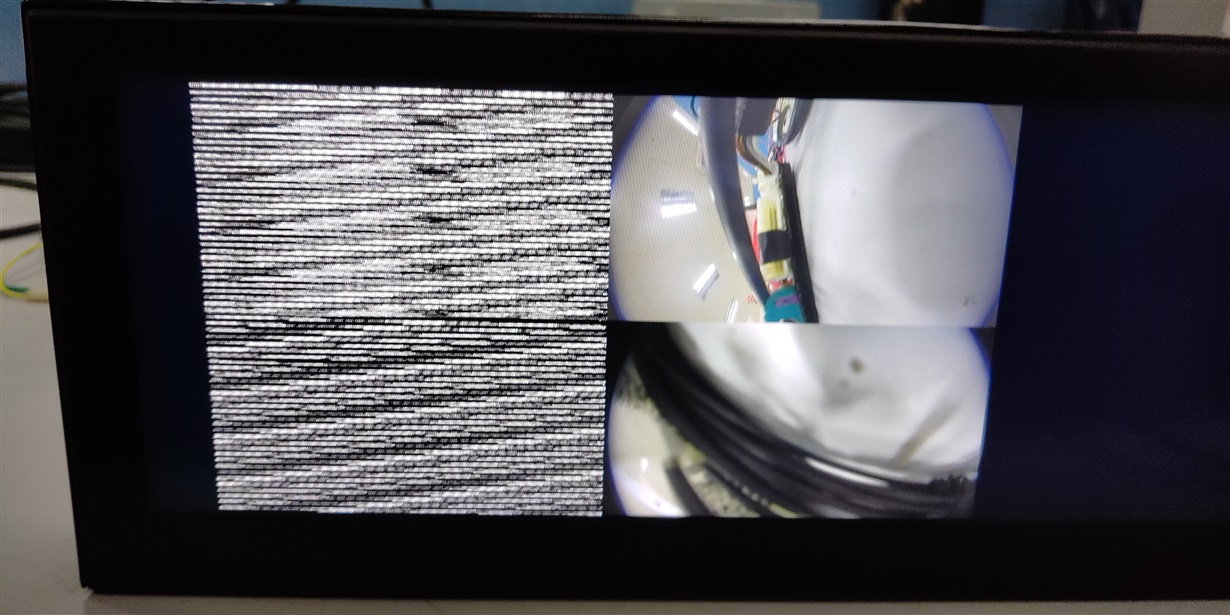

Here is the display:

How can I get all four lanes into color bar mode without using CSI Replicate Mode(0x21)?

Best regards,

Tzung