Part Number: DP83TC811SEVM

Other Parts Discussed in Thread: DP83TC811EVM

Tool/software: Linux

Hi, Ti,

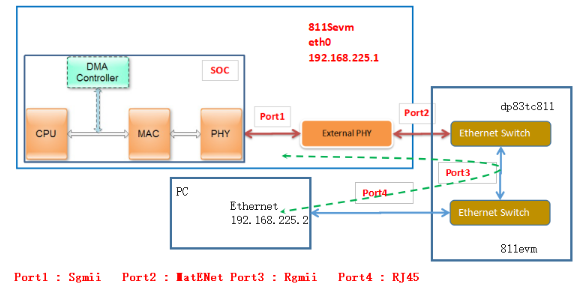

We are using qcom mdm9607 to connect to DP83TC811SEVM, control connected by MDC / MDIO, and data connected by SGMII.

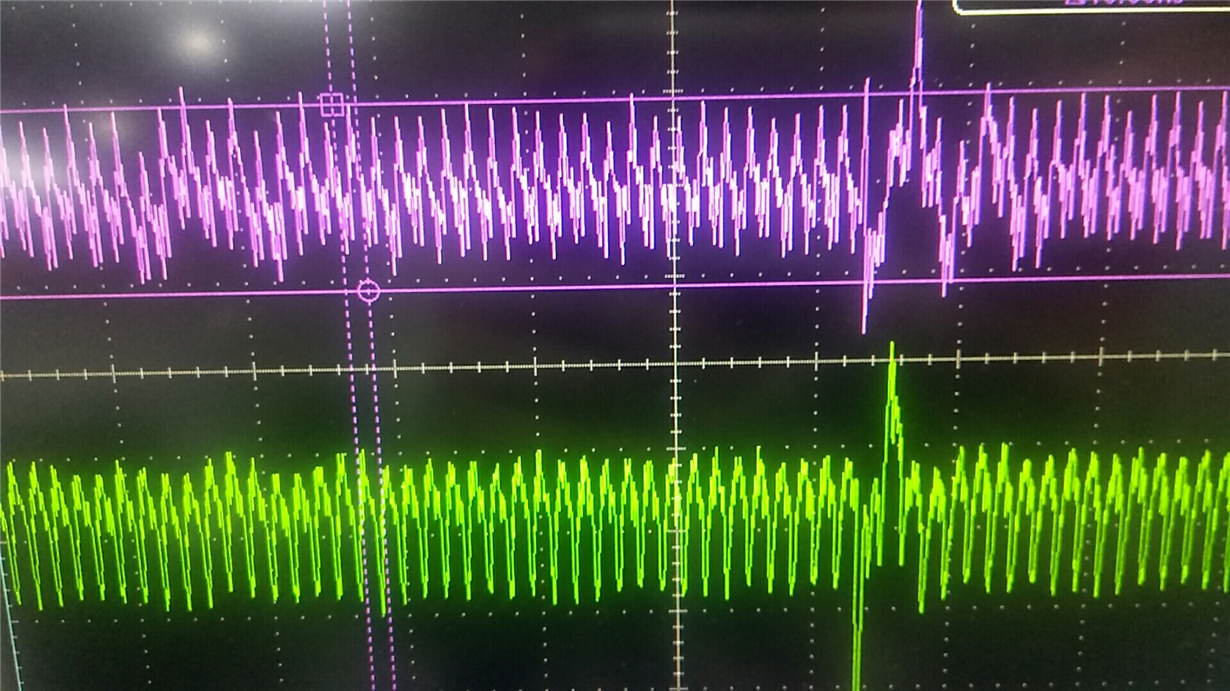

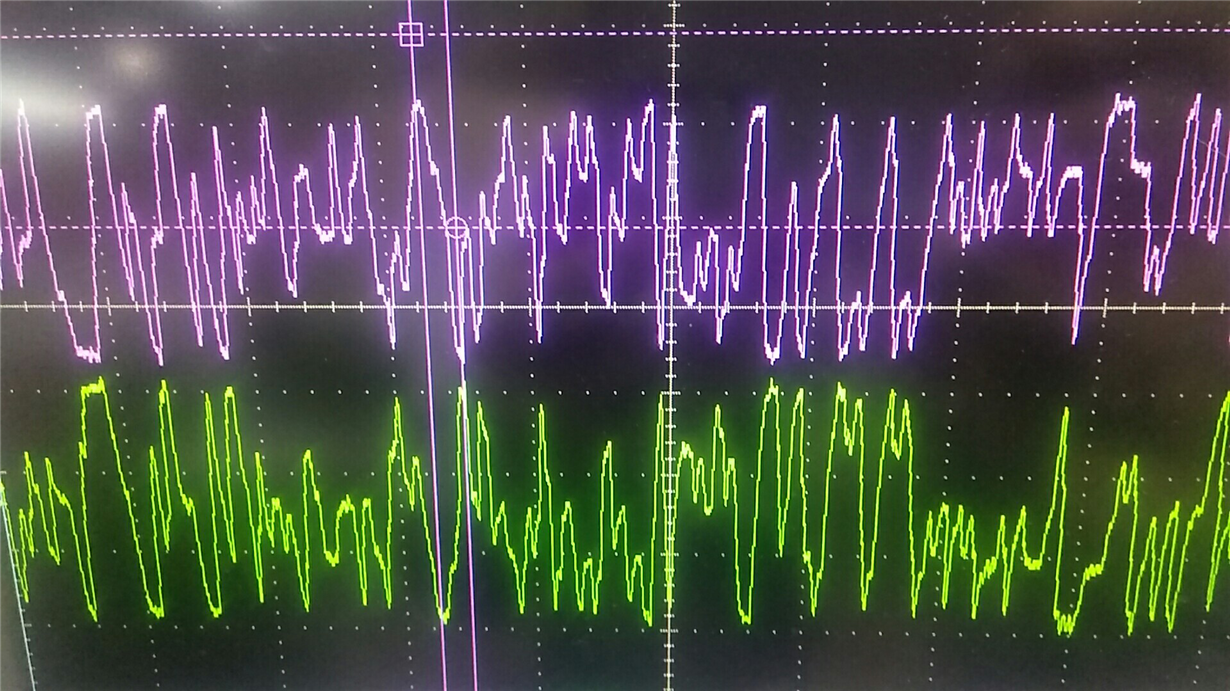

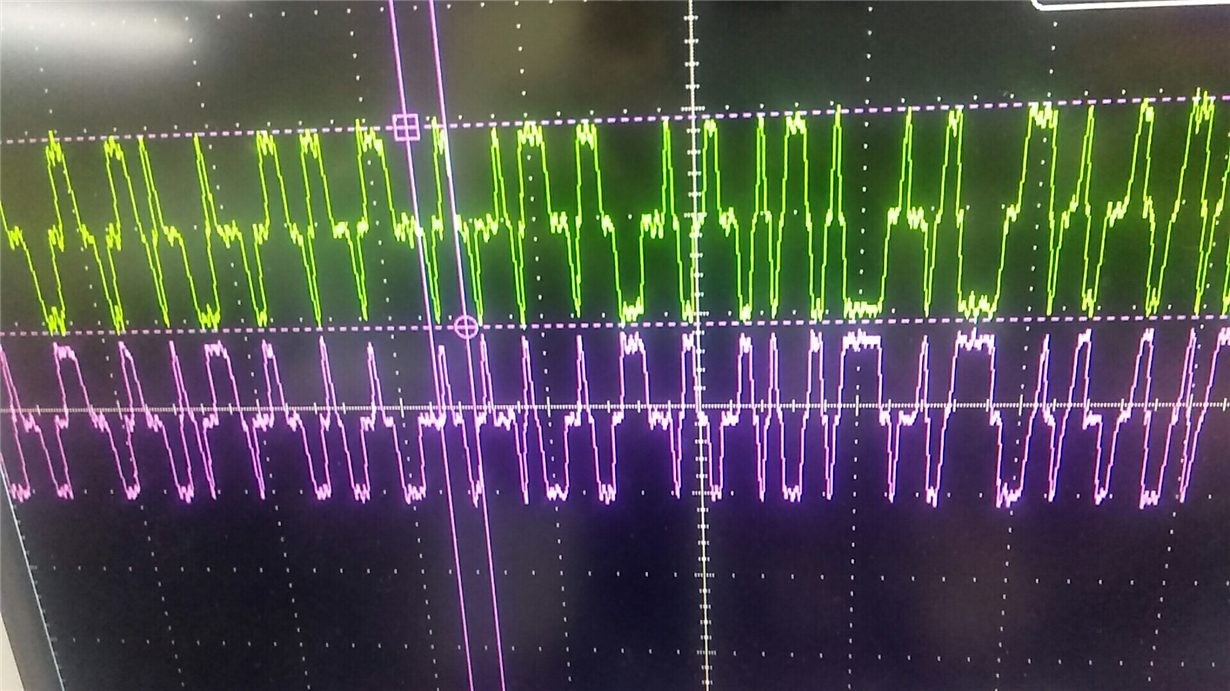

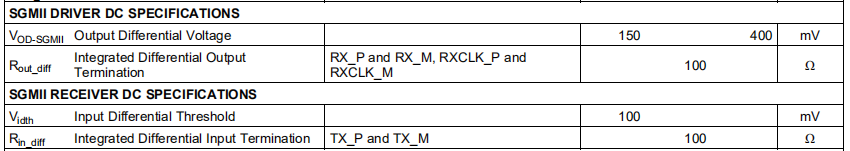

From SOC SGMII port we use osciloscope to catch driver signal, it's 62.5MHz and peak to peak is only 200mv or so.

Ping from SOC to PC or from PC to SOC, it's no respond.

Please let me know if this signal is OK.

Regards,