Part Number: TCA9517A

Other Parts Discussed in Thread: TCA9617B

Hi Team

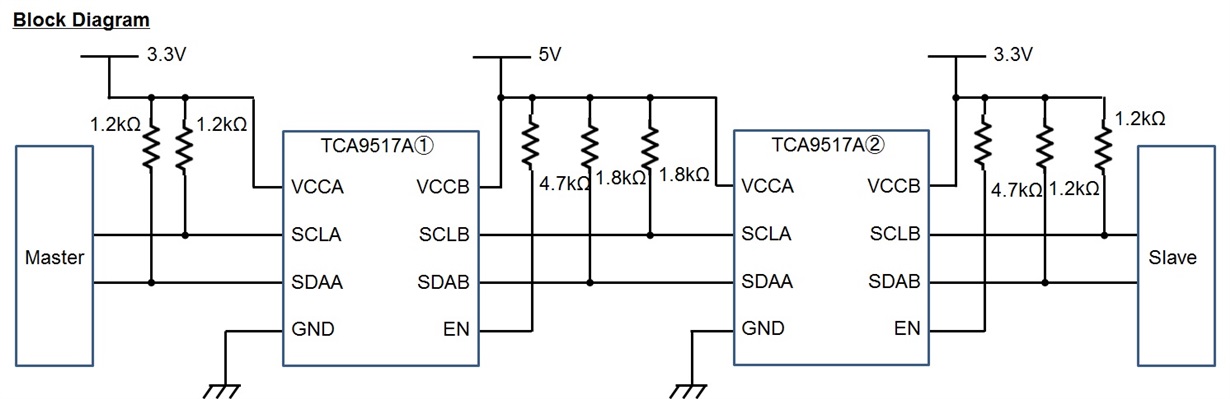

Customers are using the configuration for TCA9517A shown below.

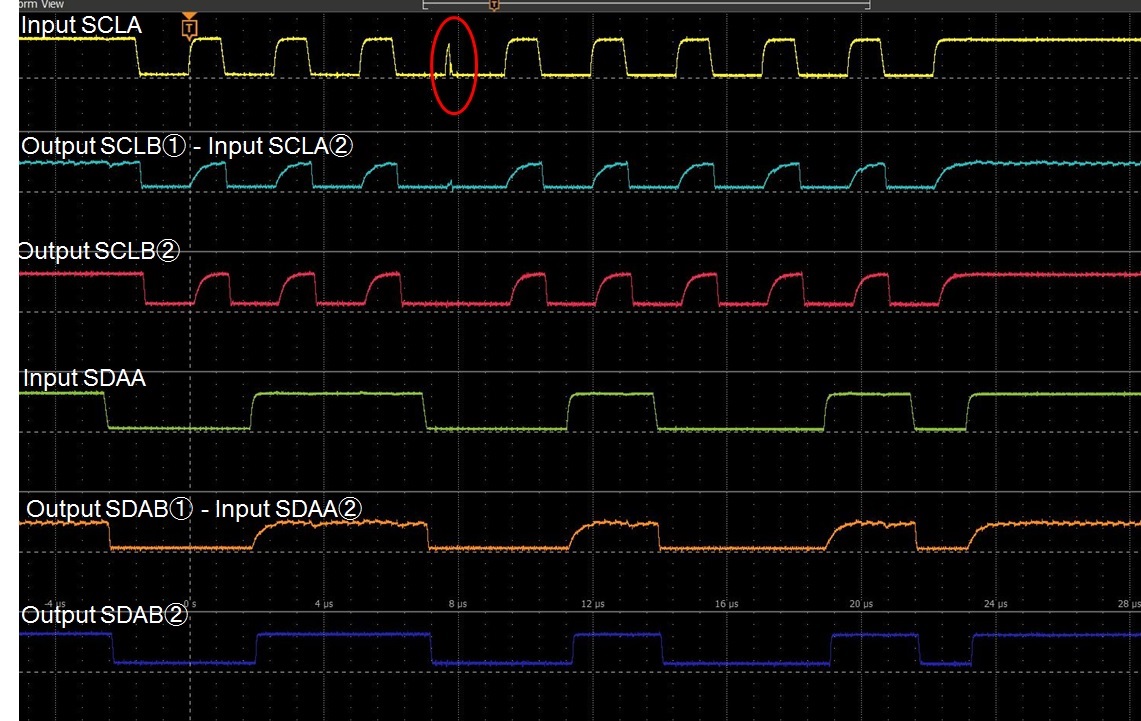

In that case, the waveform is as follows.

Input CLK is not input correctly. There may be a problem on the Master side.

But when using TCA9617B in the same configuration, the waveform was normal.

Do you know the cause? Are the input and output pull-up resistors appropriate?

The customer is in trouble and is rushing to find out the cause.

We need your support.

Best Regards,

Ishiwata