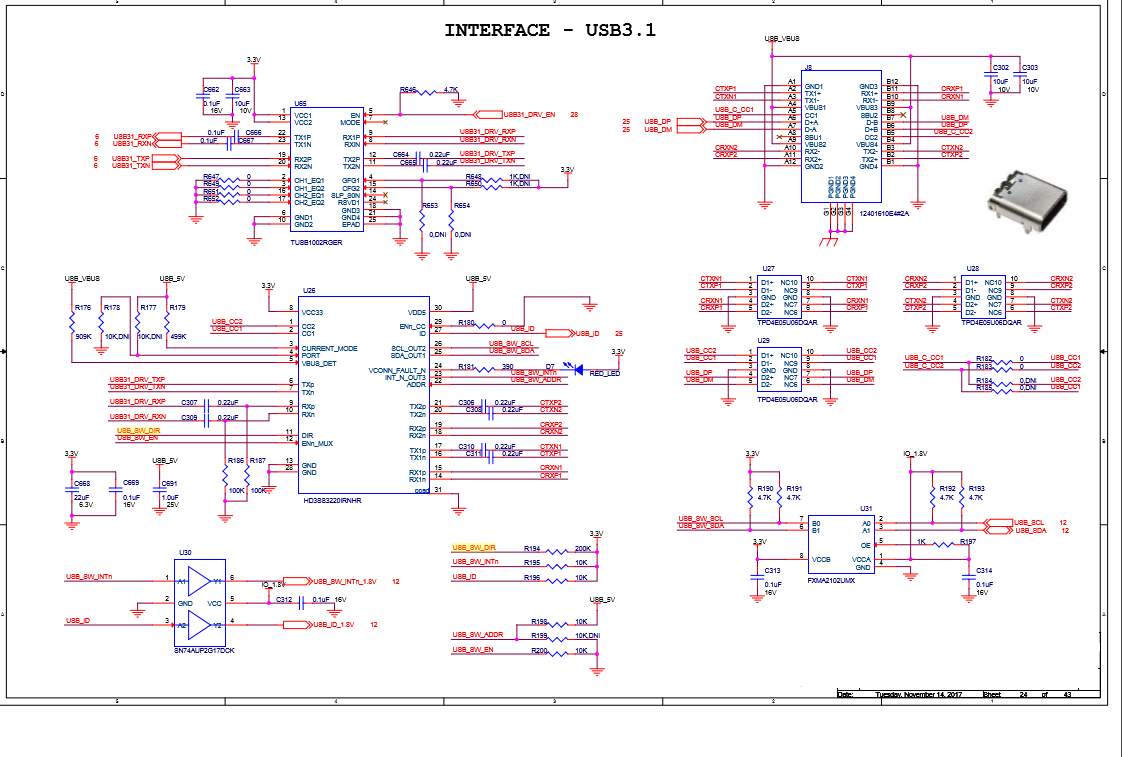

Part Number: HD3SS3220

Other Parts Discussed in Thread: TUSB1002, TUSB1002A

Hi,

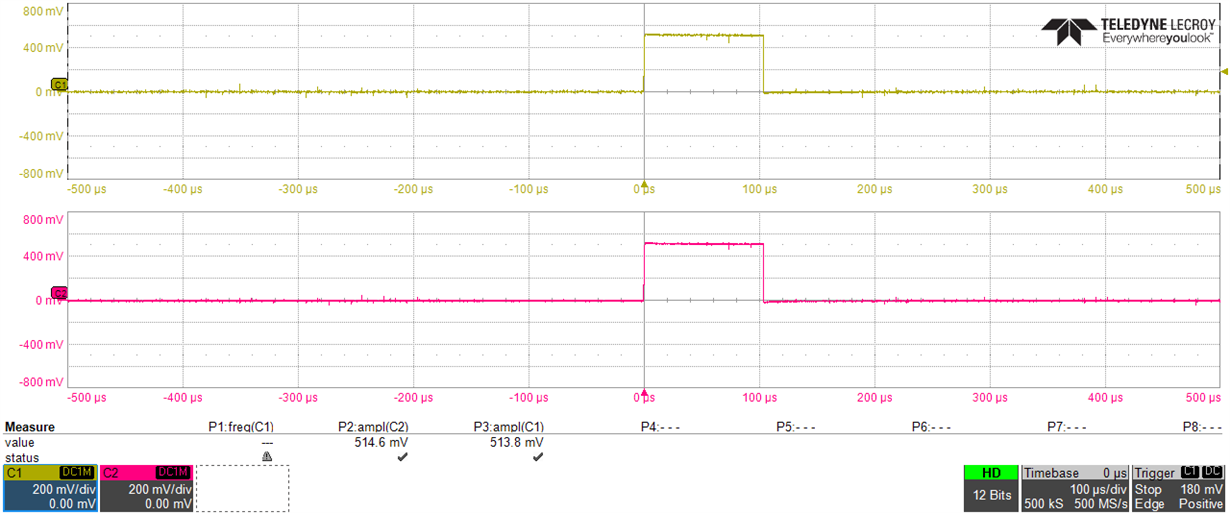

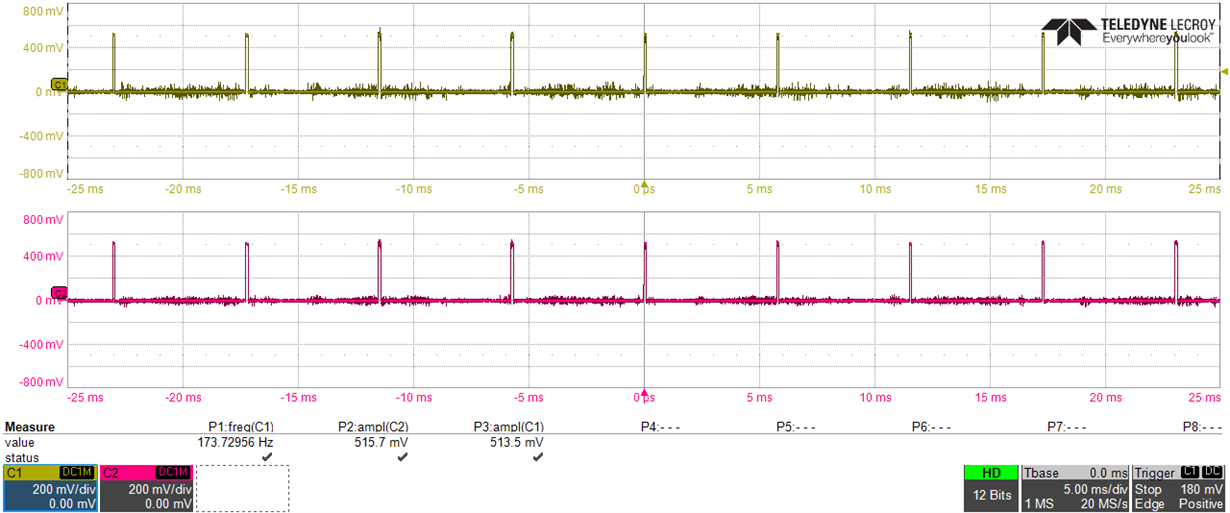

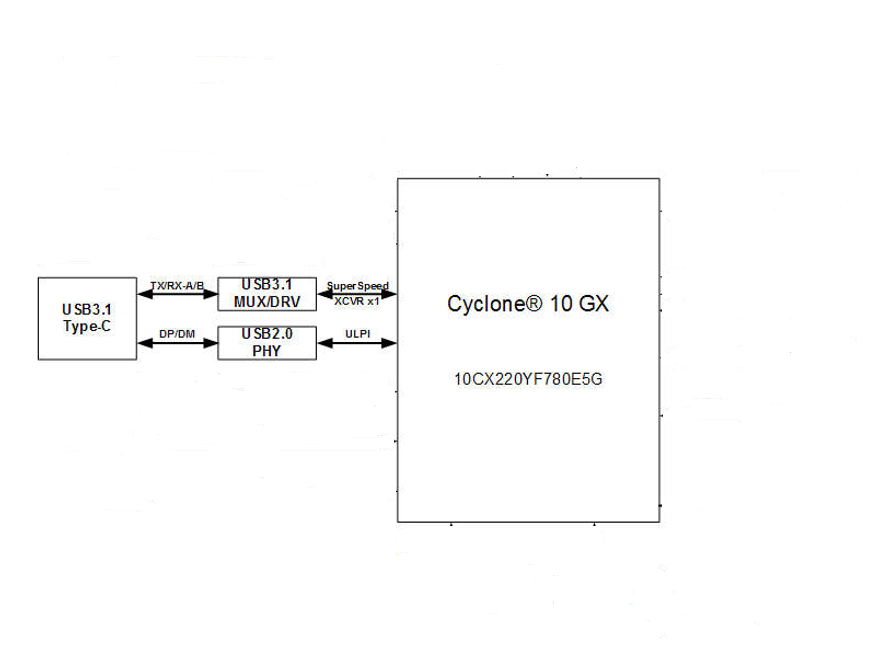

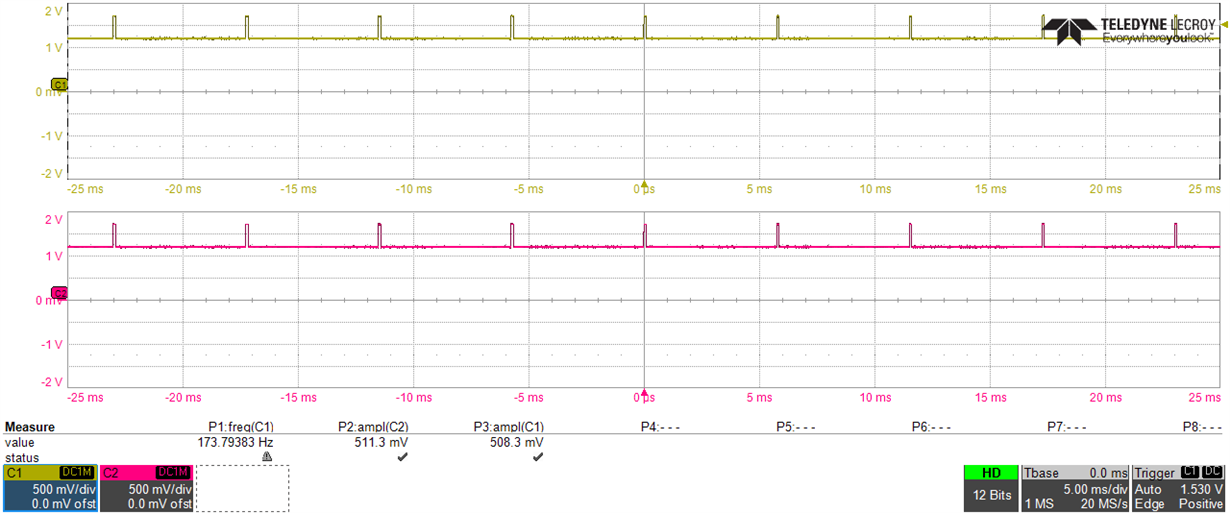

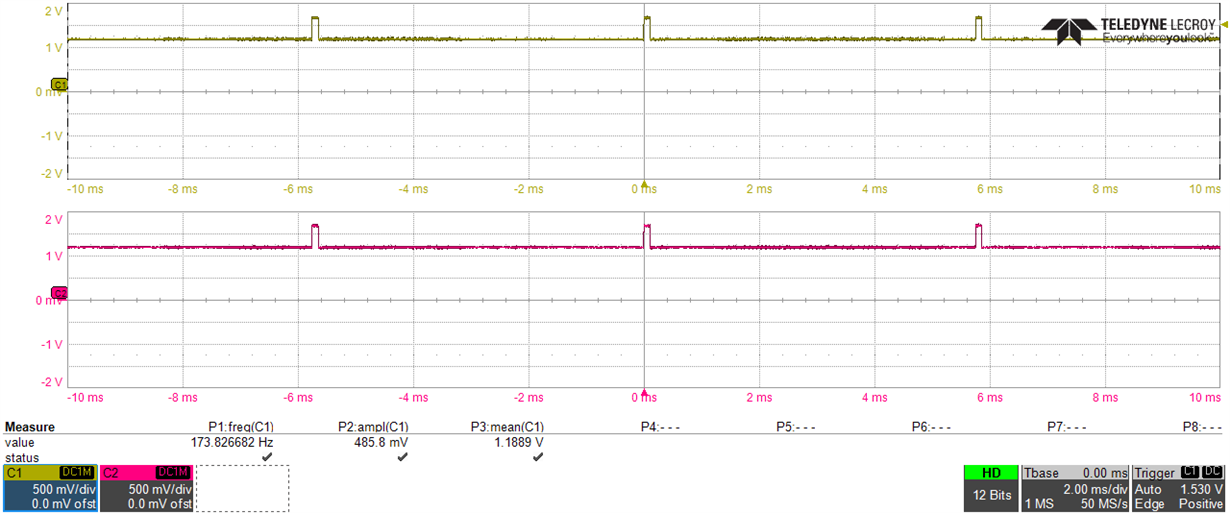

I'm having an issue with the HD3SS3220 USB controller. When reading the connection status register at address 0x09, the value returned is always 00100000 which indicates that the device is not yet attached even though it's connected to a USB 3.0 port. On power up, how long do I have to wait before being able to communicate via I2C with the device controller? according to the datasheet on page 18, it states and I quote "The HD3SS3220 local I2C interface is available for reading/writing after x clock cycles when the device is powered up". What is exactly should this x clock cycle value be? why is it that the HD3SS3220 cannot sense it's already connected.. do I have to manually set it's connection status?

Is anyone else having similar connection status issues?

regards,

Luis Gonzalez

Beckman Coulter, Inc