Other Parts Discussed in Thread: TCA9548A

Hello,

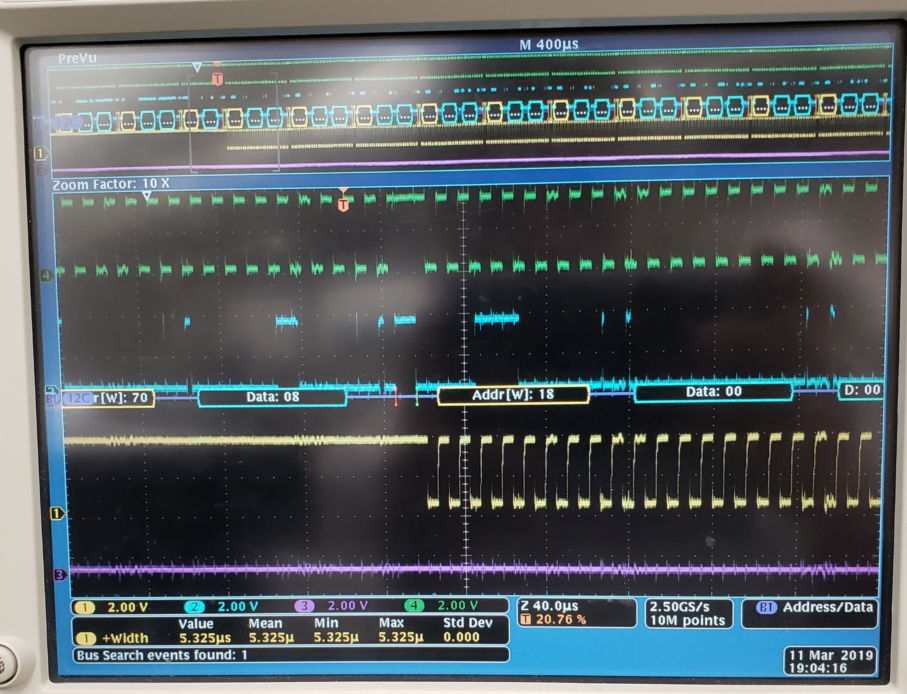

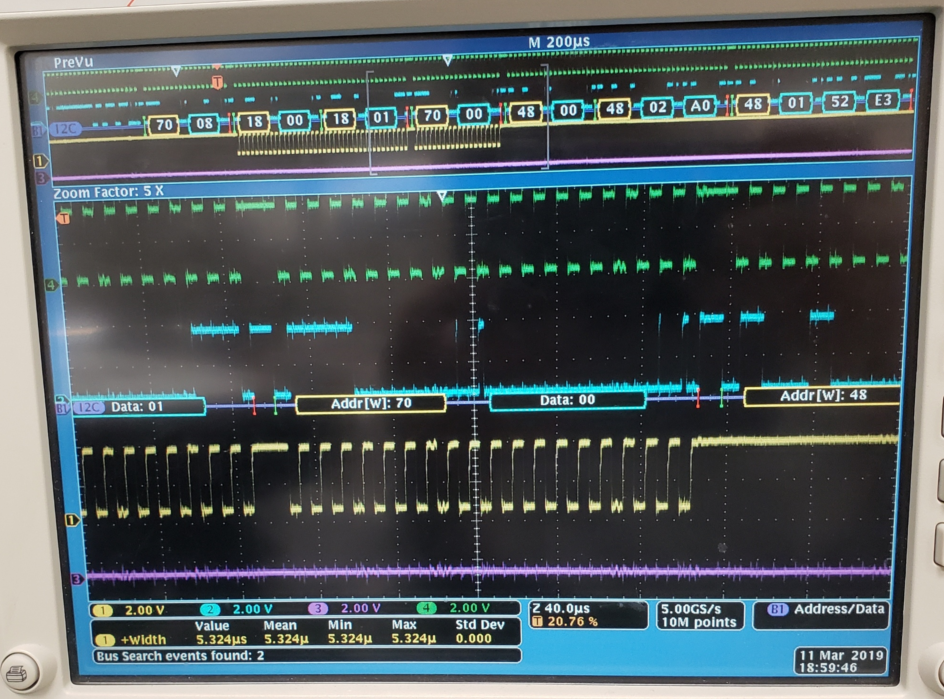

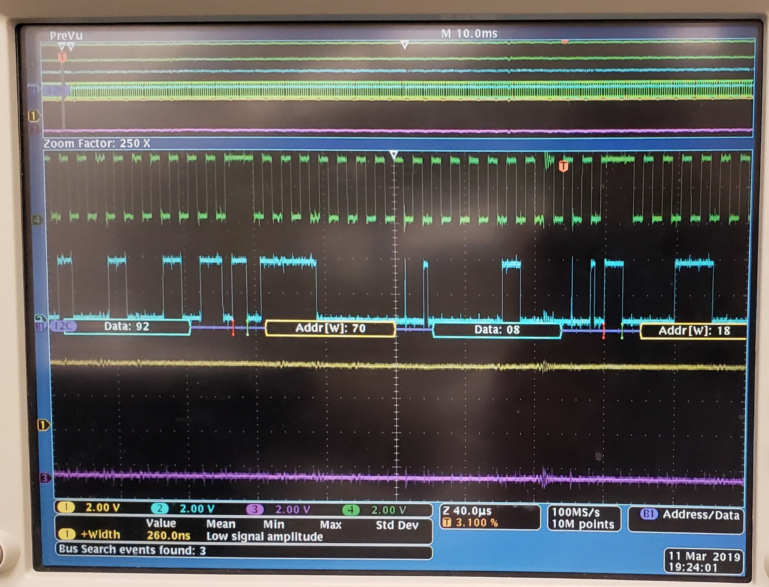

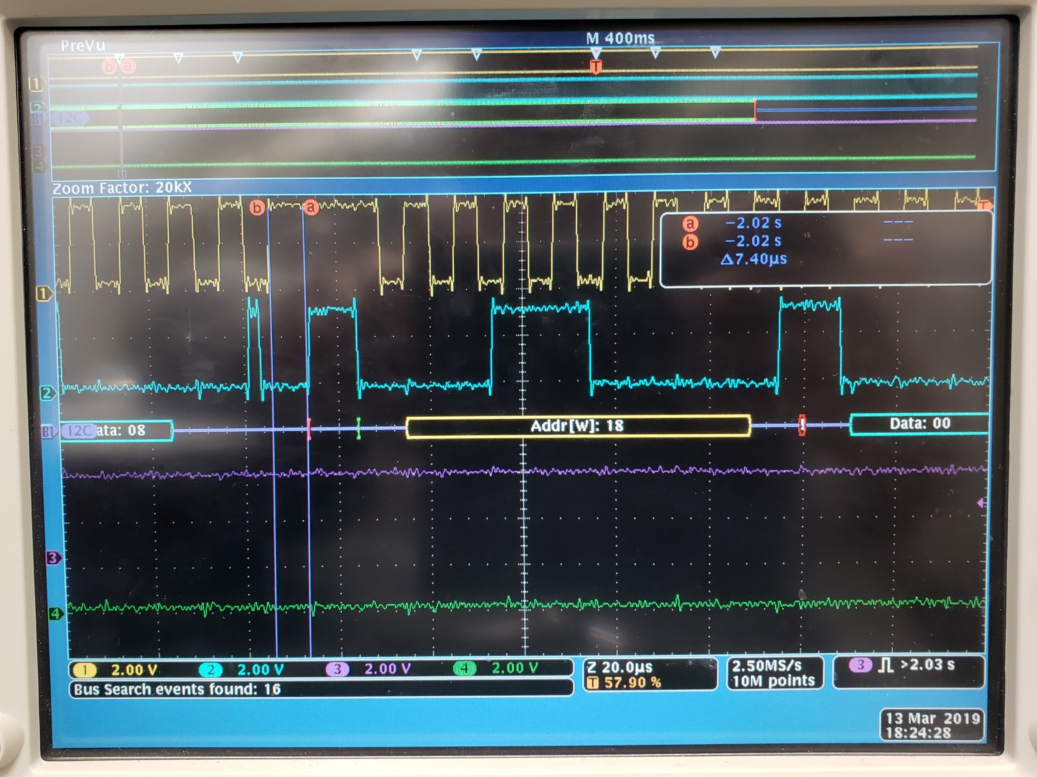

We have a system that uses the PCA9548A Switch, the device works fine most of the time however on occasion we have found that the device fails to switch. We have verified the control register is correctly set but when monitoring the SDx, and SCx lines vs the SDA and SCL we do not see data or clock. We can switch the device to another channel and then back and all is fine again. I am wondering if this is known condition and if there is an errata describing any recovery methods and also what the cause is.

Any help is appreciated.