Part Number: DS90LV804

Hello,

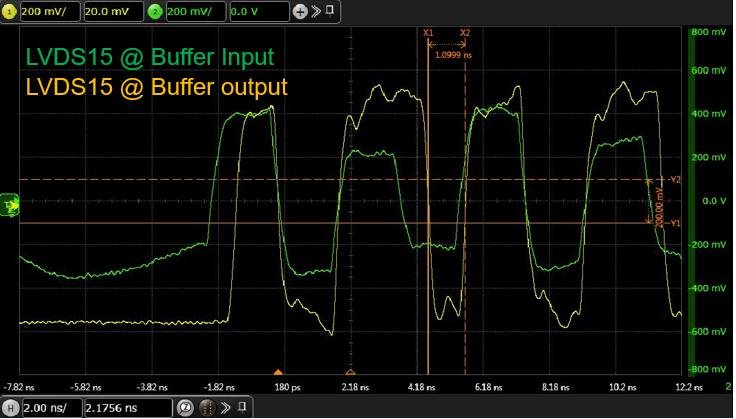

We are observing bit-errors at the output of the DS90LV804 buffer. The DS90LV804 is being driven by an FPGA. At the input of the buffer we are observing a periodic shift in the common mode voltage.

The common-mode shift period is about 150MHz, and the groups of common-mode shift pulses occur in a periodic fashion at a rate of ~350kHz. I've inserted a scope shot of the single ended signals and associated math functions here:

A few things about the signals:

- The signal is data during idle, which just happens to be 10101~

- The two signals measured are single-ended with a tight loop.

- Common mode voltage appears to swing between 500mV and 4.1V.

- The top trace is the calculated common-mode voltage (math function)

- The middle two traces are the measured IN+/- voltages

- The bottom trace is the calculated differential voltage (math function)

- Power to the DS90LV804 is @ 3.3V (nominal)

We've narrowed down where the noise could be coming from, but what we want to understand if violating the common-mode voltage in this manner has the potential to produce bit-errors like those we are seeing.

Any insight is greatly appreciated.

Don