Part Number: DS90UB928Q-Q1

Other Parts Discussed in Thread: DS90UB929-Q1, , TFP410

Hi sir.

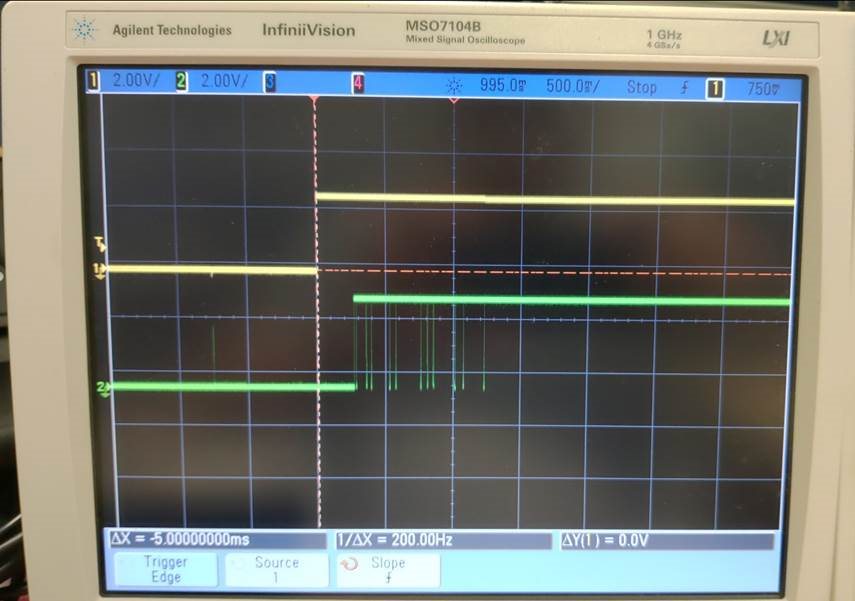

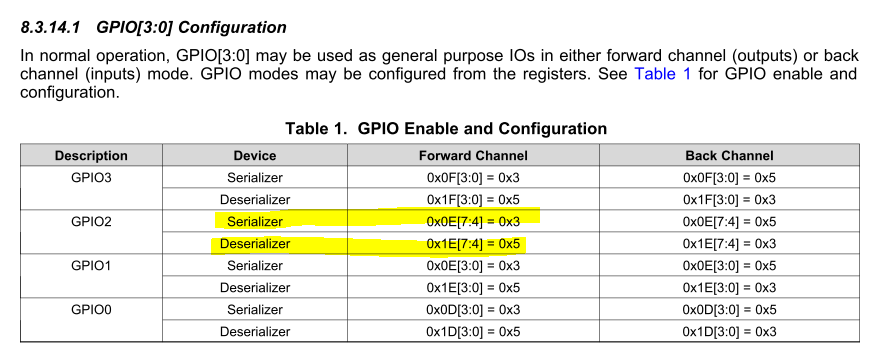

We use UB928 to set GPIO 2 to GPIO mode. But we measured the noise before setting GPIO 2 to GPIO mode.

Until UB929 and UB928 link and set to GPIO mode after about 2 seconds noise will disappear. Can this Noise be solved?

Channel 1, UB928 IDB pin(Power Enable)

Channel2, UB928 GPIO2