Hello,

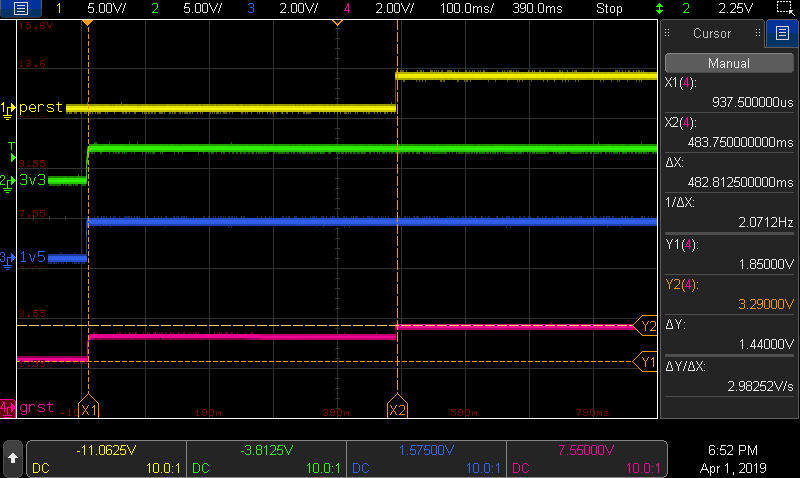

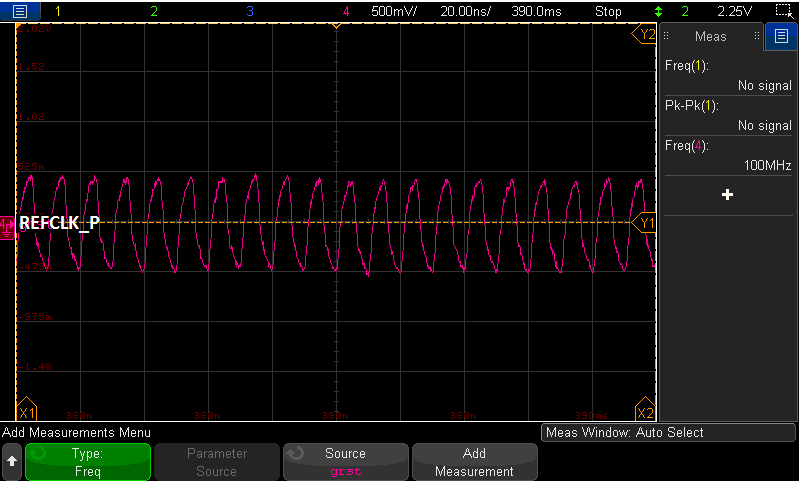

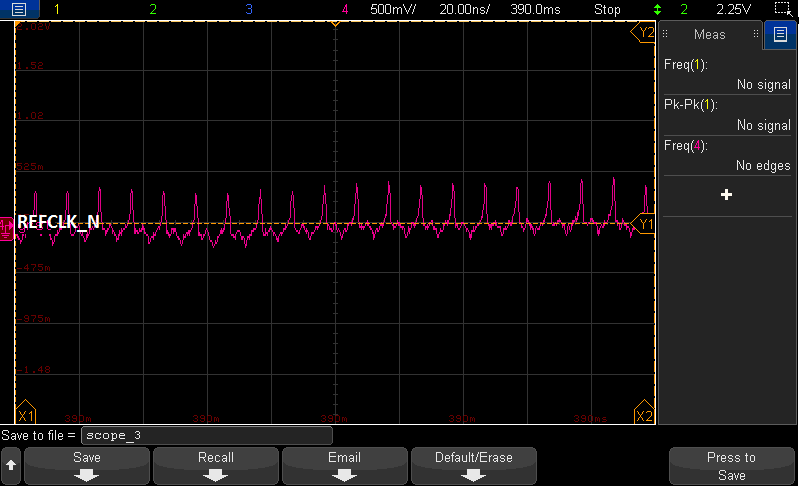

We have a design incorporating XIO2001. It is derived from XIO2001EVM. Neither linux nor windows recognized this board. Please find attached scope screenshots consisting VDD3.3V, VDD1.5V, PERST, GRST and REFCLK. Power up sequence seems ok to me except the grst which is always deassertted if 3.3Vaux is present (which is present on PC pcie connector at all times?). And one odd thing is refclk- signal (also attached as a scope screenshot).

Since XIO2001 link is not active obviously, i was not expecting any PCI clocks from it but there exist a 11 MHz square wave from PCI_CLK0.

I am also attaching schematics, a review will be much appreciated. Thank you.

Regards.

(In this image, VDD_AUX (73) connected between 0.1uF cap to gnd and 1k to Vaux, after replacing 1k with zero ohm it grst turned to be 3.3V always).