Other Parts Discussed in Thread: TMDS181

Hello,

we are trying to integrate in our FPGA kintex-7 XC7K70T-1 the Xilinx DisplayPort RX Subsystem v2.1 to receive a DP1.2 flow. (our application requires to send the flow to two MiniDisplays).

We need to use 4 lanes @5.4Gbps each.

We have designed the board from scratch, and we mounted the needed SN65DP159 following the SLLA358 application note .

But we are facing lots of issues:

1) with one board (in the following the SN02board) we are able to negotiate the DP link but with some limitations:

a) never at the maximum needed value 5.4Gbps

b) most of the time setting 2.7Gbps, connecting to a Windows 7 Dell laptop with DisplayPort on docking station; and when the link is correctly negotiated it works very well, very stable.

c) never connecting to a test pc with a NVIDIA GPU with native DisplayPort output

2) with the second board (in the following the SN04 board)

a) never, at neither 5.4Gbps or 2.7Gbps or lower

b) same situation connecting to Laptop or test pc.

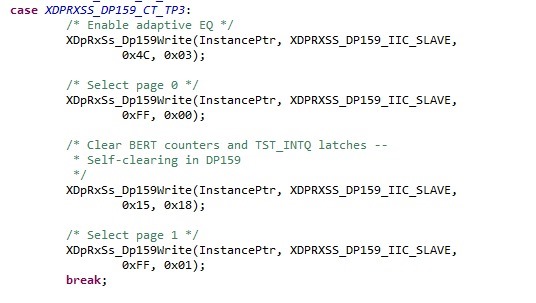

With both the SN02/SN04 boards when the link is not working we used the diagnostic command XDpRxSs_ReportDp159BitErrCount from Xilinx driver (it reads the retimer registers)

and we have seen that there are errors at the Retimer inputs (while no errors are traced when the link is established, and in fact the ink is very stable). Please check attached logs , obtained setting to 2.7Gbps to have also a working situation (both the logs are related to the SN02, nut the SN04 not ok is identical to the SN02 one).

Can someone support us?

Could some retimer configuration values be incorrect? we have followed the configuration suggested within the Xilinx reference design

What could we investigate on?

We are suspecting an issue with the retimer reset: in fact it seems that when the SN02 is correctly working, the link proceeds in working correctly if we reprogram the FPGA, even if we do this action many times. On the contrary if we power cycle the board, sometimes the link is ok and sometimes not.

Thanks a lot in advance. We are in a big hurry due to a pressing schedule

Bye

Giovanna

LOG KO

*******************************************************

Successfully ran Spi polled Example

XCLR to low

=== Initializing ===

XCLR to high

=== PS0 ===

*******************************************************

DisplayPort Pass Through Demonstration

(c) 2015 by Xilinx

System Configuration:

*******************************************************

= XDpRxSs_ReportCoreInfo =

DisplayPort RX Subsystem info:

DisplayPort Receiver(DPRX):Yes

IIC:Yes

Audio enabled:No

Max supported audio channels:2

Max supported bits per color:8

Supported color format:0

HDCP enabled:No

Max supported lane count:4

Max supported link rate:20

Multi-Stream Transport mode:No (SST)

Max number of supported streams:1

DP RX Subsystem is running in: SST with streams 1

System capabilities set to: LineRate A, LaneCount 4

**************************r*****************************************

In this configuration the RX acts as Master whilethe TX is used to

display the video that is received on RX. This mode operates on the

clock forwarded by DP159. CPLL is used for RX and TX

*******************************************************************

VPHY PLS 0

VPHY PLS 0

RX Link & Lane Capability is set to A, 4

-----------------------------------------------------

-- DisplayPort RX-TX Demo Menu --

-----------------------------------------------------

Select option

1 = Change Lane and Link capabilities

2 = Link, MSA and Error Status

3 = Toggle HPD to ask for Retraining

4 = Restart TX path

5 = Switch TX data to internal pattern generator

6 = Switch TX back to RX video data

w = Sink register write

r = Sink register read

z = Display this menu again

x = Return to Main menu

-----------------------------------------------------

Please plug in RX cable to initiate training...

VPHY PLS 0

Dprx_InterruptHandlerPwr

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 0

BERT counter0[11:8] : 0

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT c

-------------------

log OK

-------------

*******************************************************

Successfully ran Spi polled Example

XCLR to low

=== Initializing ===

XCLR to high

=== PS0 ===

*******************************************************

DisplayPort Pass Through Demonstration

(c) 2015 by Xilinx

System Configuration:

*******************************************************

= XDpRxSs_ReportCoreInfo =

DisplayPort RX Subsystem info:

DisplayPort Receiver(DPRX):Yes

IIC:Yes

Audio enabled:No

Max supported audio channels:2

Max supported bits per color:8

Supported color format:0

HDCP enabled:No

Max supported lane count:4

Max supported link rate:20

Multi-Stream Transport mode:No (SST)

Max number of supported streams:1

DP RX Subsystem is running in: SST with streams 1

System capabilities set to: LineRate A, LaneCount 4

**************************r*****************************************

In this configuration the RX acts as Master whilethe TX is used to

display the video that is received on RX. This mode operates on the

clock forwarded by DP159. CPLL is used for RX and TX

*******************************************************************

VPHY PLS 0

VPHY PLS 0

RX Link & Lane Capability is set to A, 4

-----------------------------------------------------

-- DisplayPort RX-TX Demo Menu --

-----------------------------------------------------

Select option

1 = Change Lane and Link capabilities

2 = Link, MSA and Error Status

3 = Toggle HPD to ask for Retraining

4 = Restart TX path

5 = Switch TX data to internal pattern generator

6 = Switch TX back to RX video data

w = Sink register write

r = Sink register read

z = Display this menu again

x = Return to Main menu

-----------------------------------------------------

Please plug in RX cable to initiate training...

VPHY PLS 0

Dprx_InterruptHandlerPwr

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 0

BERT counter0[11:8] : 0

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Dprx_InterruptHandlerTrainingDone

> Interrupt: Training done !!!(BW: 0xA, Lanes: 0x4, Status: 0x77;0x77).

Dprx_InterruptHandlerNoVideo

Dprx_InterruptHandlerVideo

20 vblanks

200 vblanks

= XDpRxSs_ReportLinkInfo =

LINK_BW_SET (0x400) status in DPCD = 0xA

LANE_COUNT_SET (0x404) status in DPCD = 0x4

LANE0_1_STATUS (0x043C) in DPCD = 0x77

LANE2_3_STATUS (0x440) in DPCD = 0x77

SYM_ERR_CNT01 (0x448) = 0x80008000

SYM_ERR_CNT23 (0x44C) = 0xFFFFFFFF

PHY_STATUS (0x208) = 0xF000FF

= XDpRxSs_ReportMsaInfo =

RX MSA registers:

Clocks, H Total (0x510) : 1800

Clocks, V Total (0x524) : 1375

HSyncPolarity (0x504) : 0

VSyncPolarity (0x518) : 0

HSync Width (0x508) : 16

VSync Width (0x51C) : 5

Horz Resolution (0x500) : 1600

Vert Resolution (0x514) : 1200

Horz Start (0x50C) : 48

Vert Start (0x520) : 119

Misc0 (0x528) : 0x00000021

Misc1 (0x52C) : 0x00000000

User Pixel Width (0x010) : 4

M Vid (0x530) : 288358

N Vid (0x534) : 524288

M Aud (0x324) : 0

N Aud (0x328) : 0

VB-ID (0x538) : 16

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 0

BERT counter0[7:0] : 0

BERT counter0[11:8] : 0

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

*** Detected resolution: 1600 x 1200***

cycle 0

Dprx_InterruptHandlerVideo

Dprx_InterruptHandlerVideo

Dprx_InterruptHandlerVideo

*** Detected resolution: 1600 x 1200 @ 60Hz, BPC = 8, Color = 0***

Selecting Format 1 4:3 24bit RGB 60.00P

modeline 1600 1200 1800 1375 152 134 16 5 32 36 48 0.323 60.00 12.121 148.500 4Lane x 2

SPI_CHECK failed offset 0x07, Expected 0x10, Read 0x00

SPI_CHECK failed offset 0x33, Expected 0x67, Read 0x74

SPI_CHECK failed offset 0x80, Expected 0x00, Read 0x01

SPI_CHECK failed offset 0x81, Expected 0x00, Read 0x81

SPI_CHECK failed offset 0x9A, Expected 0x0F, Read 0x00

Wait about 1000 us

=== PS1 ===

=== PS2 ===

=== PS cancel ===

*******************************************************

Successfully ran Spi polled Example

XCLR to low

=== Initializing ===

XCLR to high

=== PS0 ===

*******************************************************

DisplayPort Pass Through Demonstration

(c) 2015 by Xilinx

System Configuration:

*******************************************************

= XDpRxSs_ReportCoreInfo =

DisplayPort RX Subsystem info:

DisplayPort Receiver(DPRX):Yes

IIC:Yes

Audio enabled:No

Max supported audio channels:2

Max supported bits per color:8

Supported color format:0

HDCP enabled:No

Max supported lane count:4

Max supported link rate:20

Multi-Stream Transport mode:No (SST)

Max number of supported streams:1

DP RX Subsystem is running in: SST with streams 1

System capabilities set to: LineRate A, LaneCount 4

**************************r*****************************************

In this configuration the RX acts as Master whilethe TX is used to

display the video that is received on RX. This mode operates on the

clock forwarded by DP159. CPLL is used for RX and TX

*******************************************************************

VPHY PLS 0

VPHY PLS 0

RX Link & Lane Capability is set to A, 4

-----------------------------------------------------

-- DisplayPort RX-TX Demo Menu --

-----------------------------------------------------

Select option

1 = Change Lane and Link capabilities

2 = Link, MSA and Error Status

3 = Toggle HPD to ask for Retraining

4 = Restart TX path

5 = Switch TX data to internal pattern generator

6 = Switch TX back to RX video data

w = Sink register write

r = Sink register read

z = Display this menu again

x = Return to Main menu

-----------------------------------------------------

Please plug in RX cable to initiate training...

VPHY PLS 0

Dprx_InterruptHandlerPwr

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 0

BERT counter0[11:8] : 0

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0x6,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT counter2[7:0] : 0

BERT counter2[11:8] : 0

BERT counter3[7:0] : 0

BERT counter3[11:8] : 0

Dprx_InterruptHandlerPllReset

0 0

Link Rate: 0xA,Lane count: 4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS : 64

TST_INT/Q : 16

BERT counter0[7:0] : 255

BERT counter0[11:8] : 15

BERT counter1[7:0] : 0

BERT counter1[11:8] : 0

BERT c