Hello Team,

I have a question which is very important for my design.

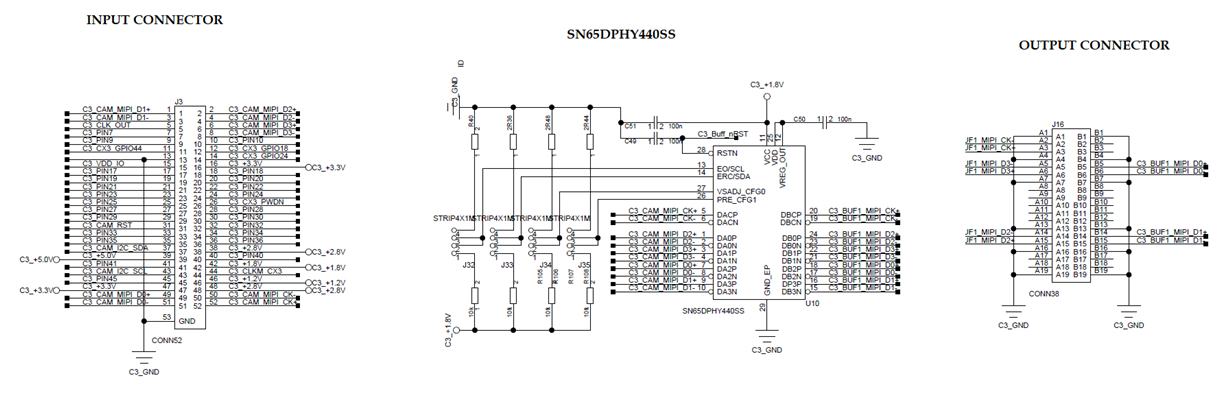

for a better routing reason, it would be great to connect the four lanes of any camera to the input of the sn65dphy440ss device with a different sequence.

Let's say, the connector from which I get the four lanes of a camera (0..1..2..3) are connected to the input of the sn65dphy440ss device to the following ports: 2..3..0..1, while the clock lane has not been changed of course.

i try to summarize here below the connection:

Camera Connector TI Buffer In TI Buffer Out Receiver

Lane0 --------------------------Lane2_in------Lane2_out------------------Lane0

Lane1 --------------------------Lane3_in------Lane3_out------------------Lane1

Lane2 --------------------------Lane0_in------Lane0_out------------------Lane2

Lane3 --------------------------Lane1_in------Lane1_out------------------Lane3

LaneClk------------------------LaneCk_in----LaneCk_out----------------LaneClk

From the datasheet I didn't understand whether the four data inputs of the sn65dphy440ss device are equivalent or not.

Now I have designed a temporary engineering board with the above connection.

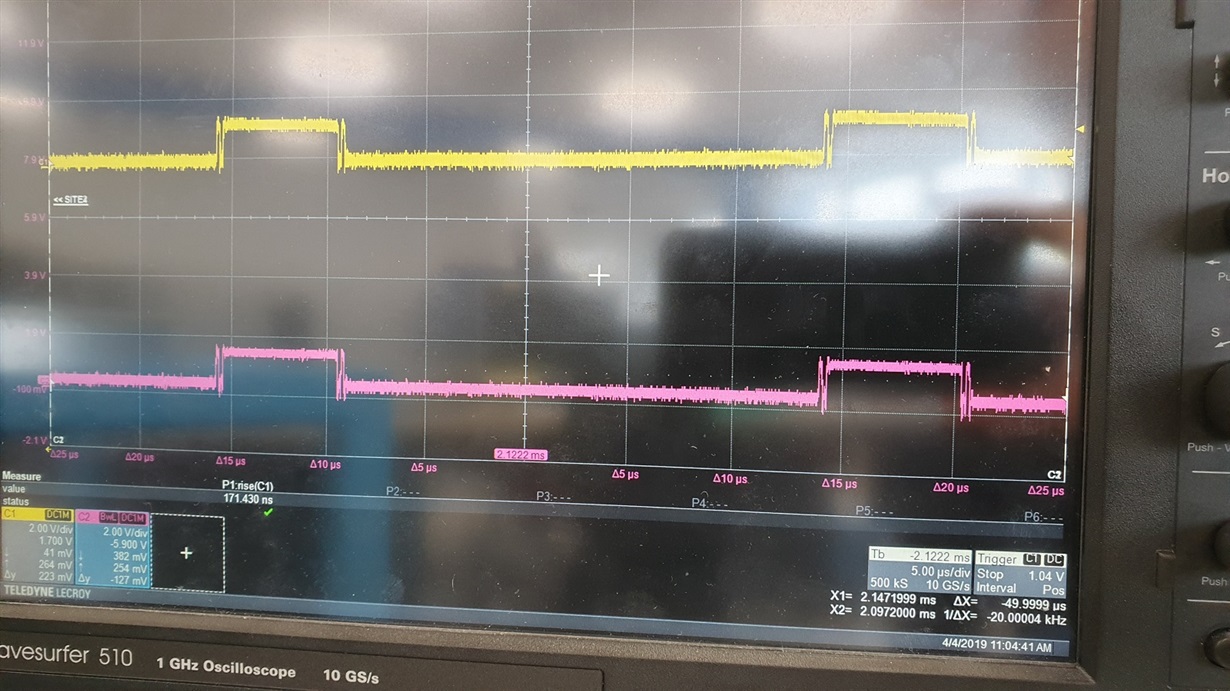

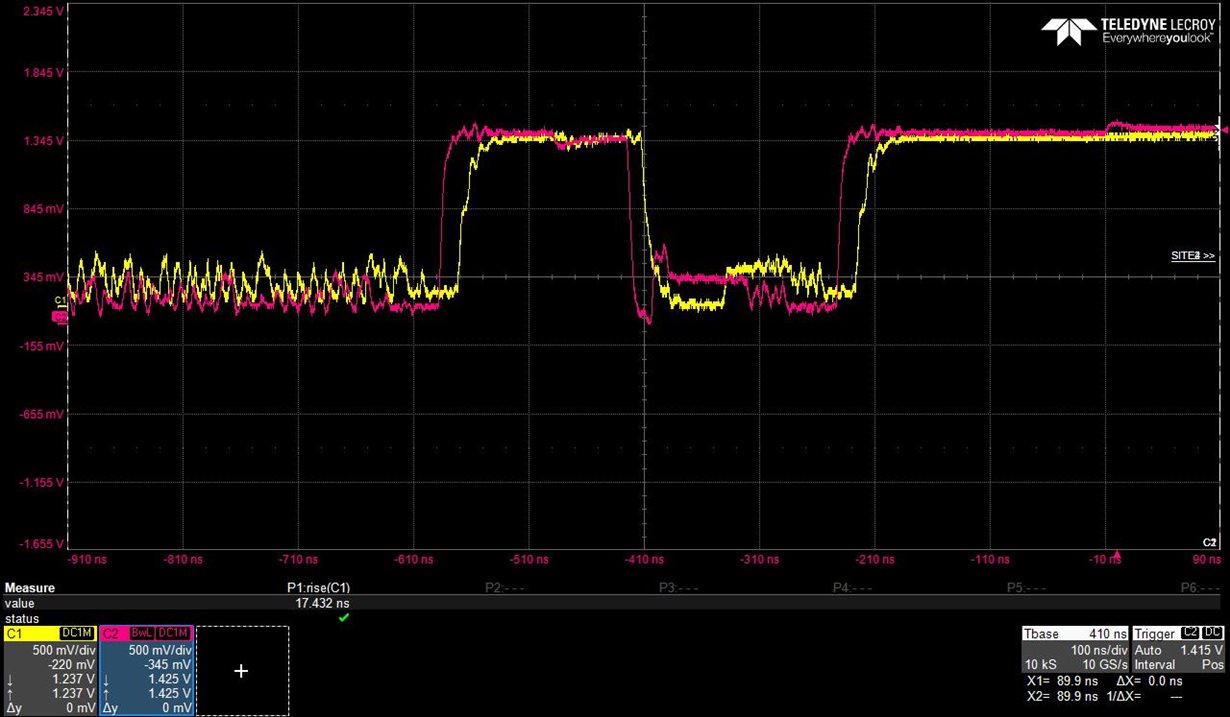

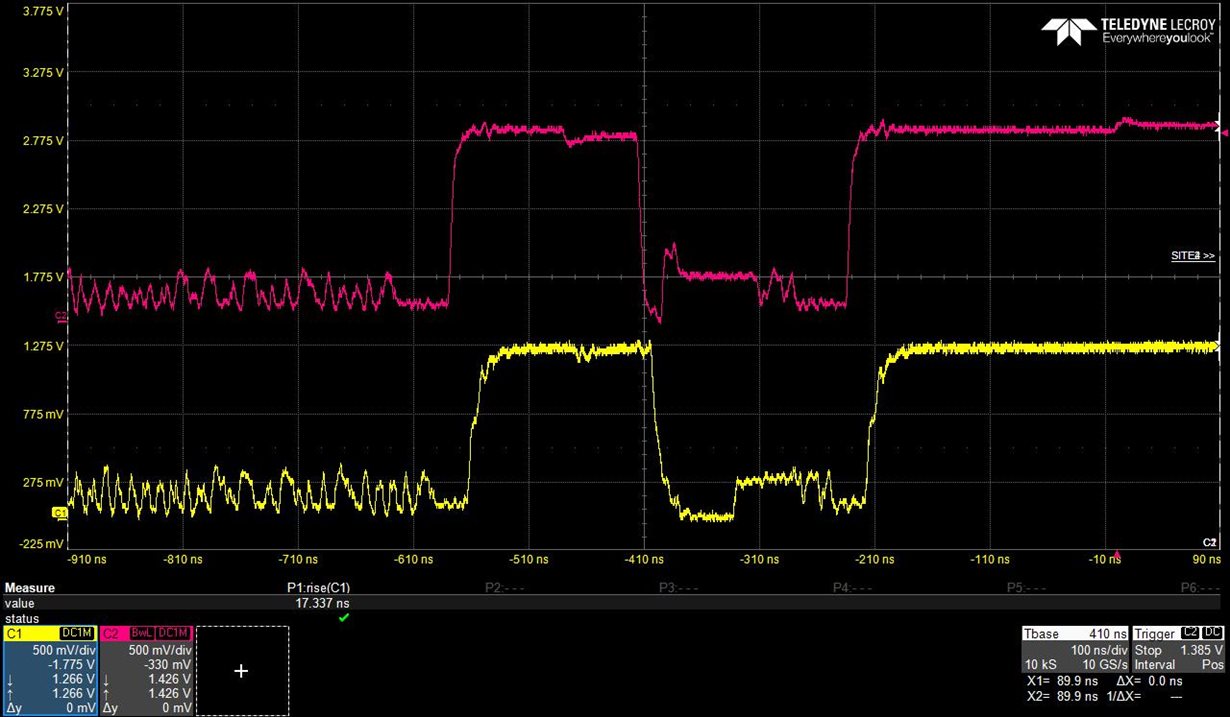

The camera used at this moment has only data0 and data 1 outputs.

these outputs are using the lane 2 and lane3, as above shown.

But unfortunately I cant get the image from the receiver.

If I connect the receiver directly to the camera, everything is working.

I hope my question is clear.

Many thanks in advance for your support

Stefano