Part Number: PCA9306

Dear Team,

We pullup SCL2/SDA2 to 3.3V. And we used 5V for both EN and Vref2.

(SCL1/SDA1 pullup to 3.3V , Vref1 3.3V)

Is there any concern of this design?

Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: PCA9306

Dear Team,

We pullup SCL2/SDA2 to 3.3V. And we used 5V for both EN and Vref2.

(SCL1/SDA1 pullup to 3.3V , Vref1 3.3V)

Is there any concern of this design?

Thank you.

Hi Bobby,

Vref1 provided by MCU card and 5V(EN & Vref2) from standby. (Our side)

Originally we provide customer SCL2&SDA2 5V system. This meet PCA9306 spec.

But customer side also have 3.3V SCL2&SDA2 system , they try and seems work currently.

So we would like to know if any concern of this design.

From PCA9306 spec , all example Vref2 & EN &SCL2&SDA2 are conneceted form Vcc2.

1>Can Vref2 & EN use 5V but Vref2 & EN pull up by 3.3V?

2>If this design have chance meet data corruption since EN 5V>3.3V+Vth

3>In such design , as in spec 8.1.5 Switch Configuration,

We should follow Figure11 [Vcc2 (5V) >Vref1(3.3V) +0.7V] or Figure 10 [Vcc2(3.3V SCL2&SDA2)=Vcc1(3.3V)]

4> If remove SDA1&SCL1 two pull up register , communication still can work.

If this removement impact such function:

Assuming the higher voltage is on the SDA2 port when the SDA2 port is high, the voltage

on the SDA1 port is limited to the voltage set by VREF1.

Or other concern on removement.

Thank you very much.

Flood

Hey Flood,

"So "the voltage on the SDA1 port is limited to the voltage set by VREF1" is protected by PCA9306(If we provide VREF1), not related to two Rpu register in Verf1?"

No, the pull up resistors provide the pull up voltage. Vref1 pin of the device is some something else in the device. It essentially provides the base voltage for the device, it does NOT provide a pull up voltage.

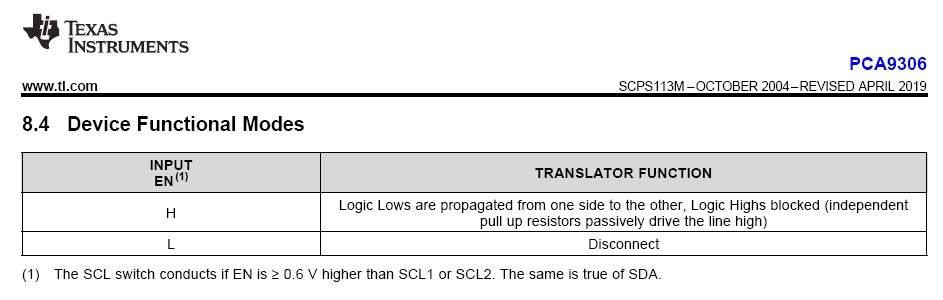

"<Spec description>EN = High =>Logic Lows are propagated from one side to the other, Logic Highs blocked"

Can you tell me where you see this in the spec? When enable is high, the SDA and SCL will pass lows. When SDA/SCL is a logic high, both sides should go up to the pull up voltage. The high is provided by the pull up resistors, the low is driven through the PCA9306 device.

"I can still measure 3.3V on SCL2 & SDA2 on PCA9306 if not connect to customer side(Without 3.3Vdpu/SCL2&SDA2 connect to nothing + With

3.3Vref1 & 5V Vref2+EN )

What connection makes SCL1 = SCL2 ?"

PCA9306 uses a pass FET architecture. The reason why you see side 2 go to 3.3V is because side 1 is pulled up to 3.3V. If you changed side 1 pull up to 2V then side 2 will go to 2V. Because you are lower than the reference voltage plus Vth, one side will mirror the other side. If you changed Vref2/EN to be 3.3V then you would see side 1 hold at 3.3V but side 2 would go to 2.7V. This is why I am suggesting you use a pull up reisstor on side 2. If you do not, you are relying on side 1 to drive the high and Vref2 to hold a stable 5V.

"If Mater SCL port low , Vref1 have current to Mater GND.How about Vdpu on other side? The current go through from PCA9306 GND or Mater GND?"

It will go through GND from the master's NFET to GND (referenced from the master). PCA9306 GND is for ESD cells in the device. It is a reference voltage to ensure body diodes do not conduct as well.

-Bobby

Hi Bobby,

1>2>3>4>5>6 understand

Thanks for reply

4> it is a strong reason to convince customer not to remove pull up register on our side1. Thanks

5> Just curious why i see 3.3V on side 2 without installing customer side.

Actually , customer will provide pull up register also.

"Blocked" confuse me on this case.

orgianl version SCL1 = SCL2, SDA1 = SDA2 seems can explain this case.

Here is the picture from spec

Thanks

Best regards,

Flood