Part Number: SN75DP130

Other Parts Discussed in Thread: HD3SS460

Hello

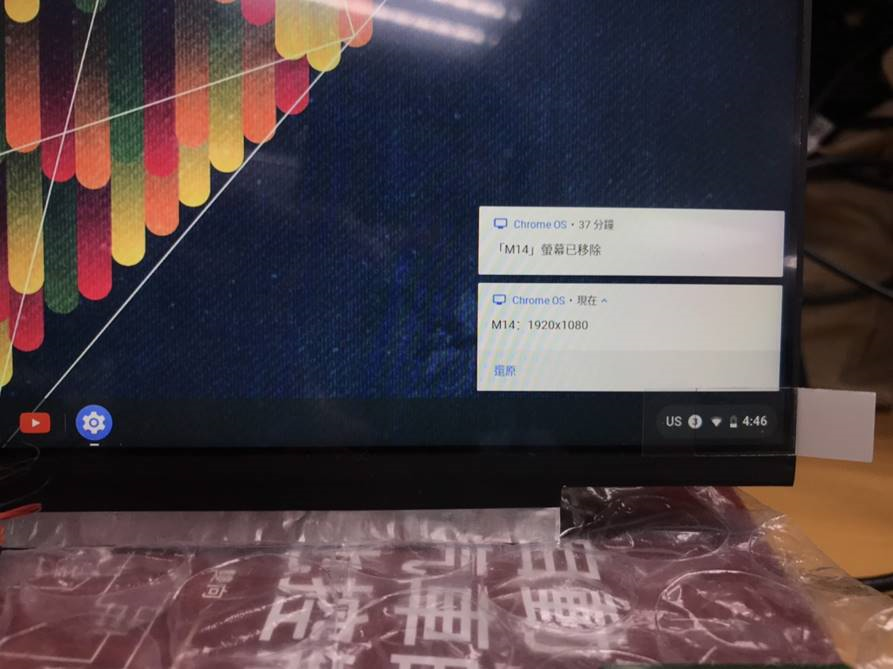

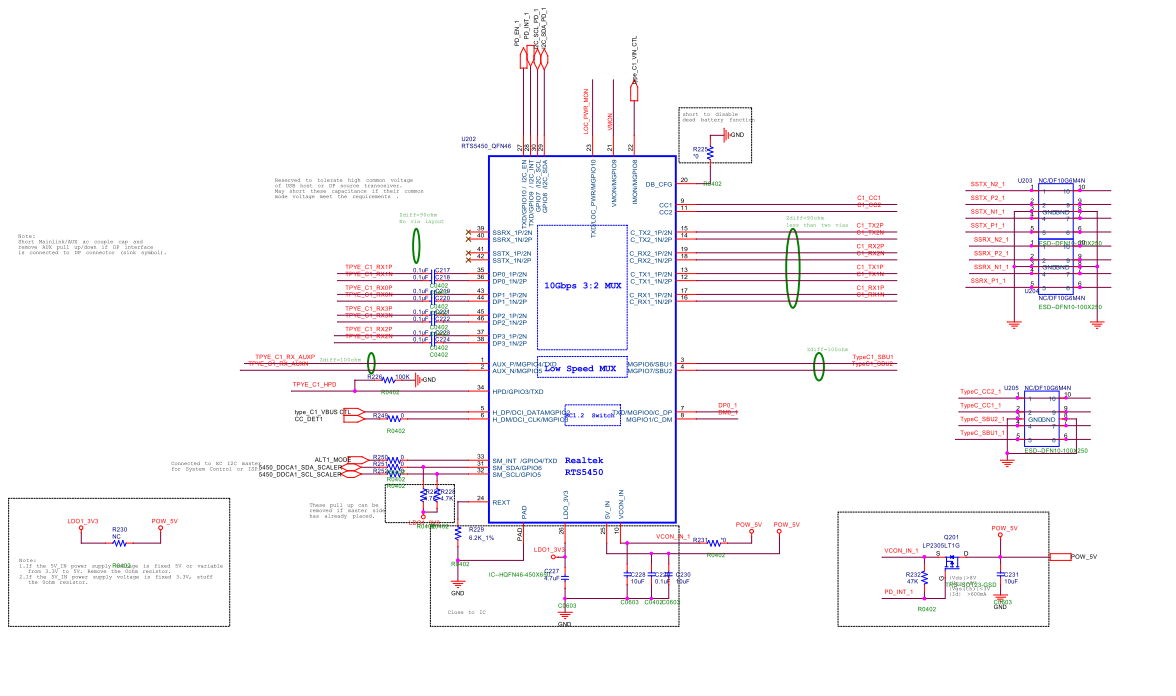

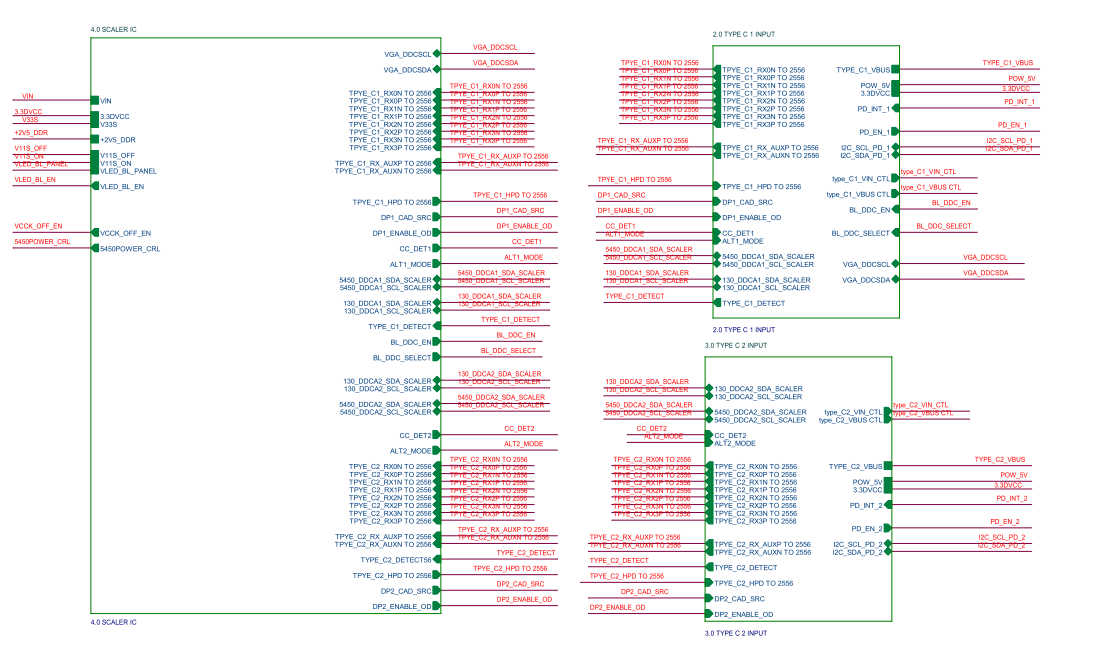

The topology is NB-> typec connector -> Mux -> DP130 -> Monitor. If NB output four lane DP, the monitor will be light up normally. But if NB output two lane or one lane DP, monitor fail to light via DP130.

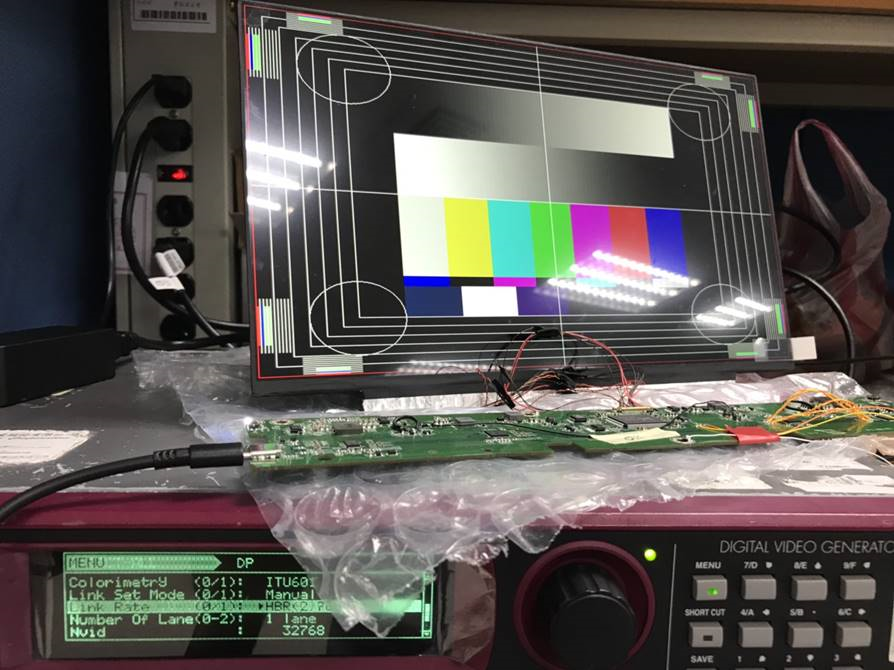

After bypass DP130, Customer use Google NB output 2 lane and 1 lane DP, the monitor will light up normally. If use Astro VG-870 (DP to Type C cable Pin assignment E), the monitor still light up normally.

Why two lane and one lane not light up monitor via DP130? Thank you.

Google NB(Chrome book)

1366x768@60Hz

Astro VG-870 (DP to Type C cable Pin assignment E)

800x600@75Hz(HBR 1 lane)

BR

Patrick