Hi teams.

My cusotmer using DP83848I in new project and encounter some package loss rate is very high. Especially in 100M communication rate.

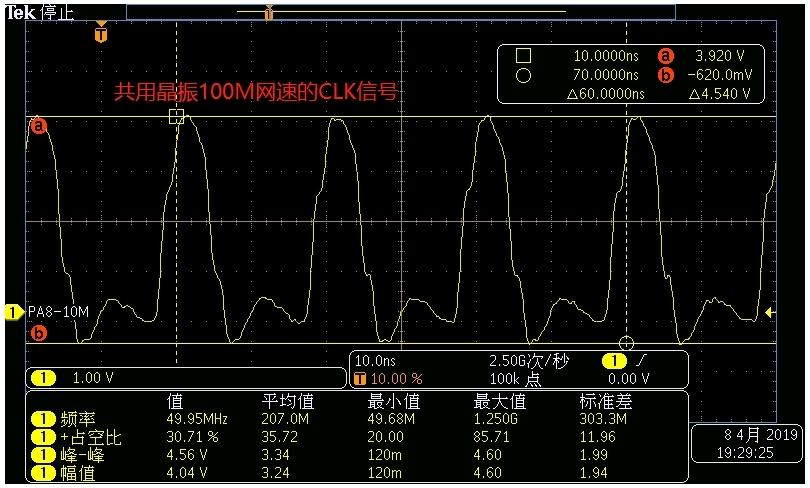

They leverage MCU output the CLK in the first. I captured the waveform from PHY side and found the CLK signal integrity is poor.

The first diagram is 100M communication rated with MCU CLK. The second diagram is 100M communication rate with an external 50M clock.

Below is my question:

- What's the common reason to cause high package loss rate? What else i should check besides the clock signal.

- In the datasheet it indicated that we need to provide a 50M clock in 100M communication rate. It mean a clock period is 20ns. But in datasheet page13. timing requirement section (T2.4.1) TX_CLK High/Low time it requires a minimum 16ns holding time. I don't understand what does it mean and how to achieve this when our period is 20ns?