Part Number: DP83867E

Team,

I have a question regarding the RGMII timing delay for the DP83867.

I am trying to understand if the delay is enabled with only using strap option without accessing the MDIO.

on the snla243 page 8 it says,

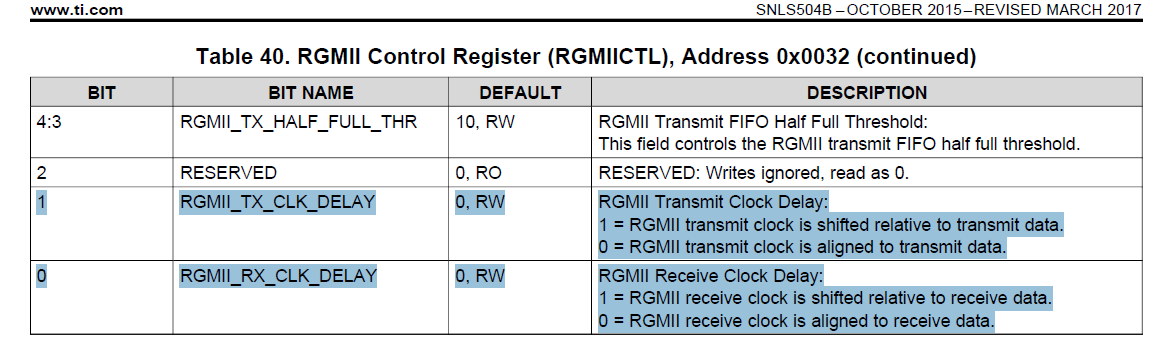

By default, RGMII RX/TX internal delays are enabled in the DP83867. To ensure the delays are

enabled, bits[1:0] of RGMII Control Register(address 0x32) should be written as 0b11.

But on the sns504b page 73 shows both tx and rx clock delay are off.