Hi teams

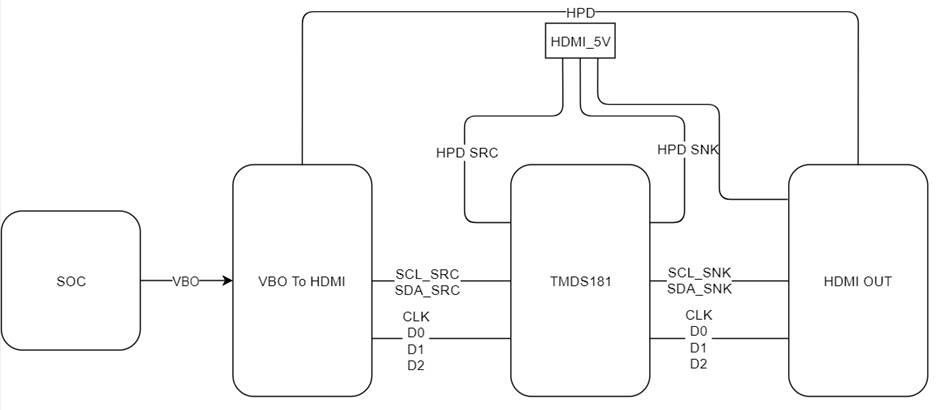

My customer is using TMDS181 in their new design and an issue has reported.

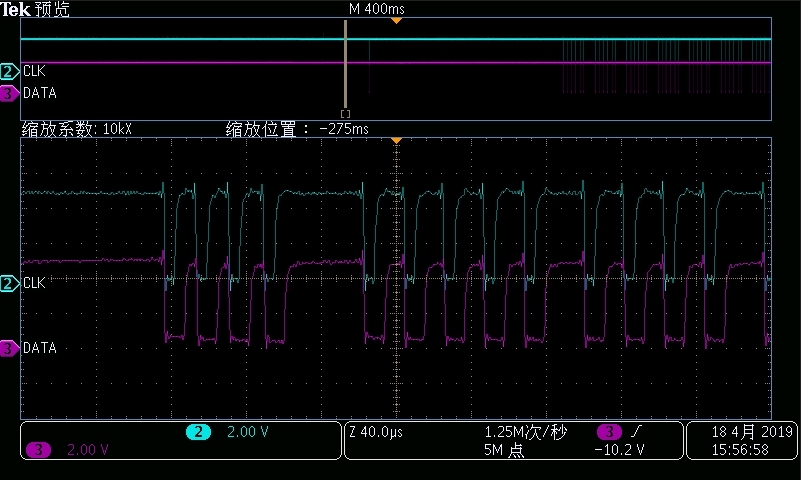

They use TMDS181 for HDMI out re-timer and found that the SCL_SNK is almost the same with SDA_SNK.

The waveform is shown below:

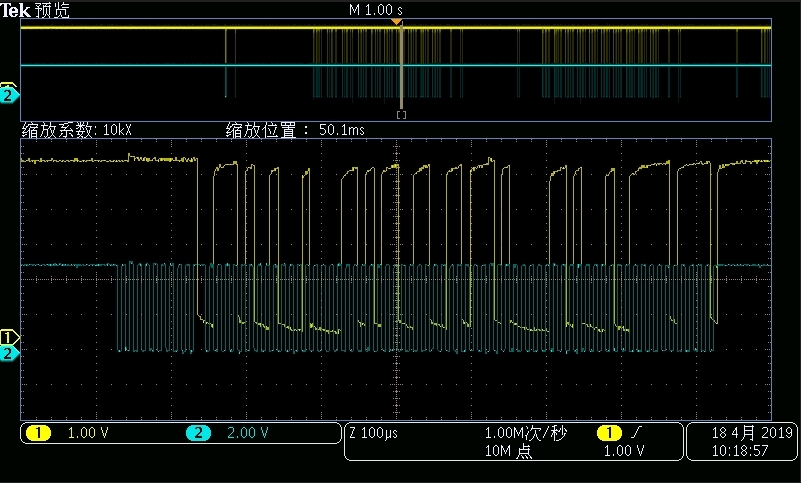

The second picture is SCL_CRC and SDA_SRC waveform.