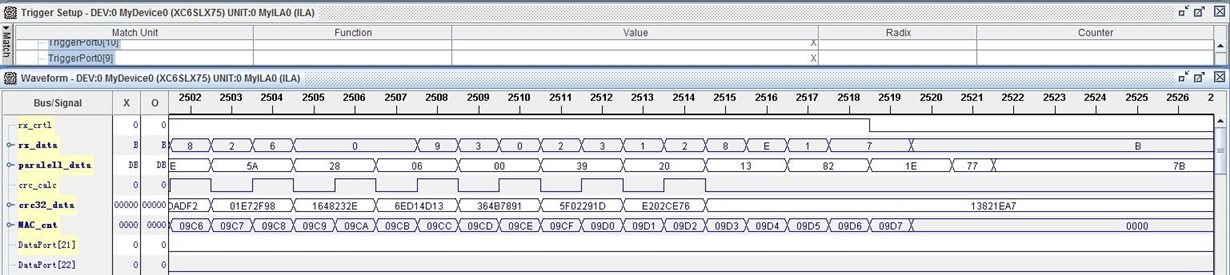

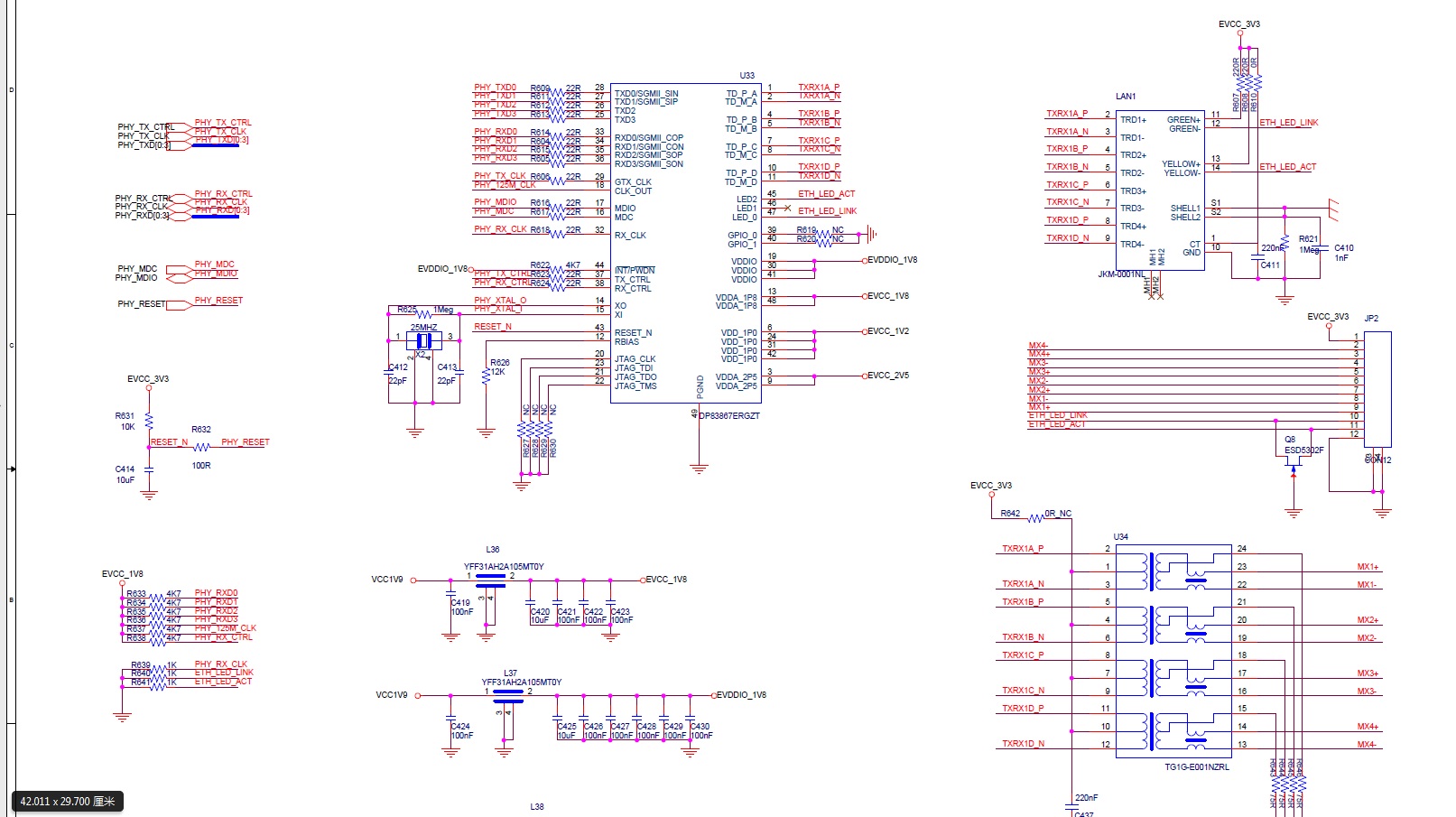

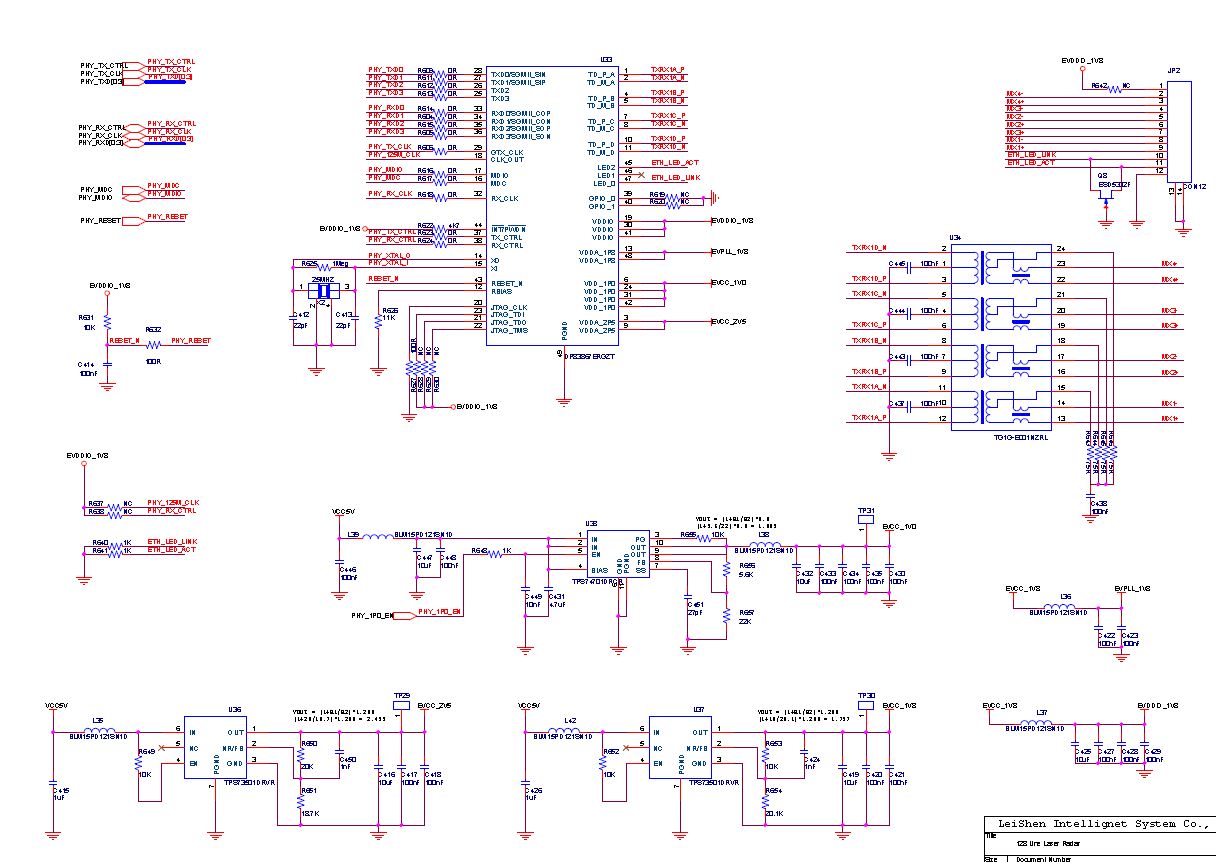

I found the DP83867E is likely to loss last CRC nibble of MAC frame in my experiment which is composed of 2 DP83867E boards. Every board has a PHY and a spartan-6 FPGA, one board sends data while another one receives. I debug the receive board FPGA with ChipScope and got the picture as attached.There is also attached the schematic for reference.

The MAC frame length is 1260bytes including the preamble and CRC bytes. So the total nibble number is 2520 , and 0x9D8 in hex. But we can see frome the picture that the MAC_cnt, the nibble counter, stops at 0x9D7, showing that the last nibble is lost. The second evidence we can get from the picture is that the calculated crc32_data is 0x13821EA7 ,which should be transmitted reverse nibbles in every byte as 0x3128E17A. The last 7 nibbles of rx_data are 0x3128E17, and the end nibble A is lost.

I guess there must be some hardware reason make my DP83867E is not working at a good condition that the last nibble is easy to be lost.Any one knows in what kind of condition that the last nibble is easy to lost?