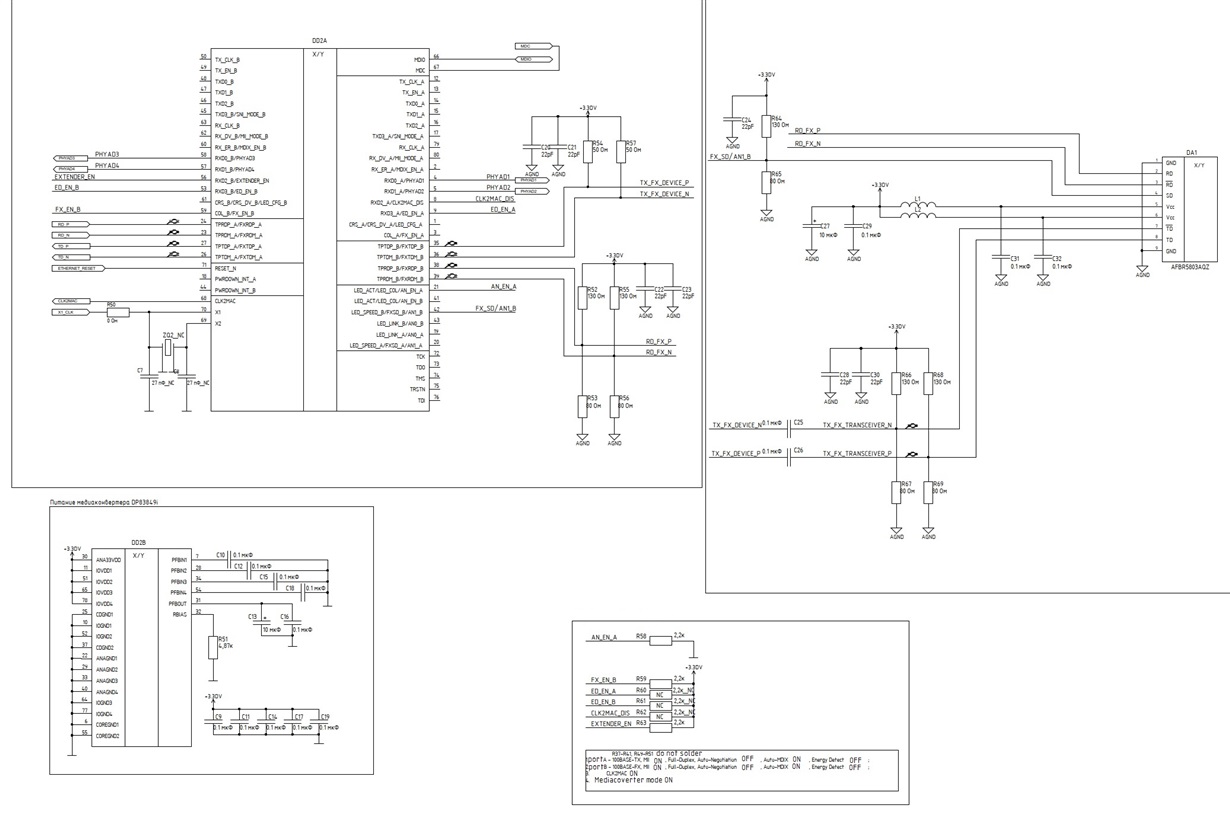

Part Number: DP83849IF

I'm building optical ethernet switch. I'm trying to use DP8384IF in media converter mode. I have several ports (several DP8384IF ICs) on my board. And I have other board with optical transiever and link status and activity leds on it (Which works fine). I've connected those boards together via optical cable. The problem is that when I power up my board link is established only half the time (sometimes it does work, but sometimes it doesn't). I'm making such conclusion according to the link status and activity leds on the other board, also when status/activity leds are off no data is being send on tx/rx diff pairs (not even idle parttern). The behavior is similiar on all DP8384IF ports exept that some ports starts even less frequently (~ 1 time out of 10). I have also have other port on my board with DP83620SQ/NOPB PHY and it works all the time. I've attached my schematic. My strap options are on the schematic. What I've checked already:

1. Clock is OK - 25 Mhz and preaty clear. (Though I don't think the clock is necessary for PHY operation cause of clock recovery, am I right by the way?)

2. Power is 3.266 V and looks pretty clear.

3. Reset is 3.3 V, active low. (Toggling reset does not help, only power cycling helps, so it is not strap options I think).

4. Also I am confused that there is no voltage on JTAG pins, pwrdown_int pins etc (they are floating on my scheme and they should have internal pull up according to datasheet).

What is going on? It seems like Port B PHY doesn't start for some reason, though I think it should it any circumstancies if there is power, pwrdown is high, reset is high (Am I right?). It looks like the PHY is in some sleep, though Energy Detect mode is of? What can be the problem? My chematic file is attached... Thanks!)