Part Number: DP83867IS

Tool/software: Linux

Hi Team,

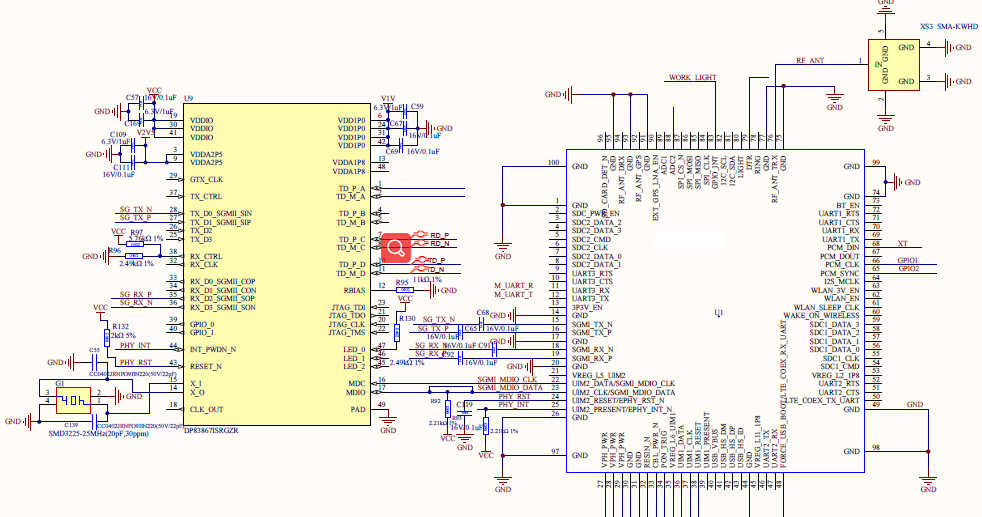

My Customer is using DP83867 with Qualcomm MDM9X07 based processor with SGMII at MAC interface. They have been able to access this PHY using MDIO , MDIO/MDC can access and read the status register.Copper interface between PHY and PC is up but not able to ping PC with the DP83848.

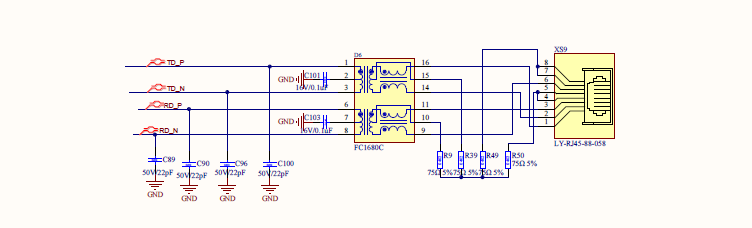

The following picture is the sch and power consumption test . I have some questions:

1. When use SGMII , is the sch correct?

2. can the linux driver from TI official (https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/about/) be uesd SGMII?

It seems that the driver is specific to RGMII. If the driver is not suitable for SGMII, are there any new drivers available?

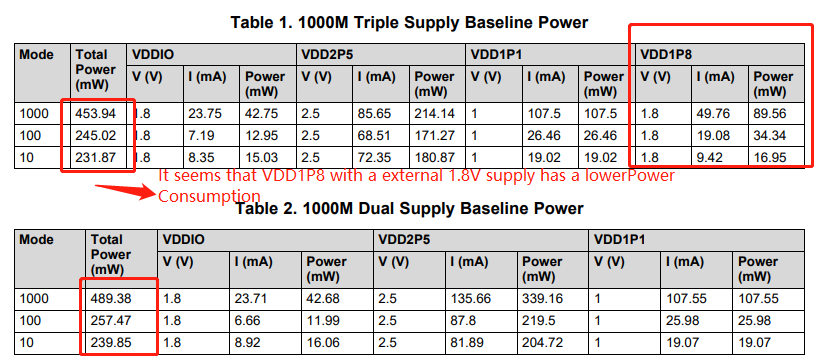

3. Whether SGMII or RGMII is used, must VDDA2P5 and VDD1P0 exist simultaneously but VDDA3 is optional?

Does VDDA3 have an external 1.8v supply that only affects the Power consumption?