Part Number: SN65DP159

hi dear supporting team,

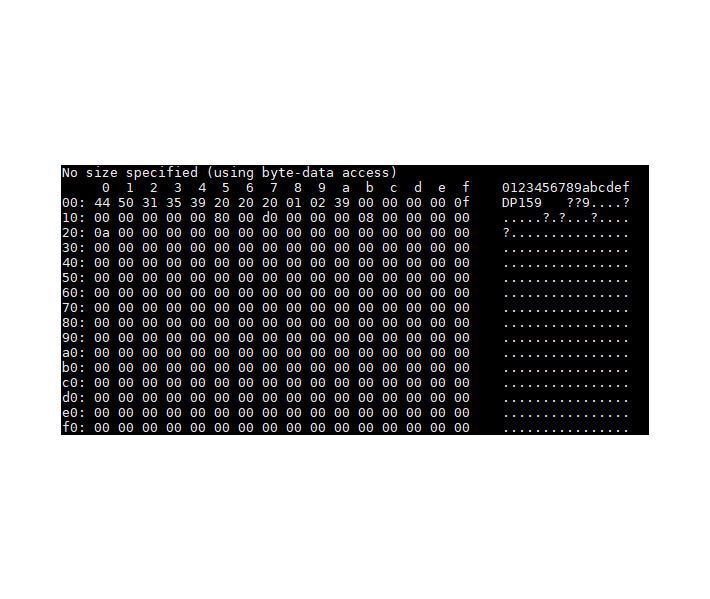

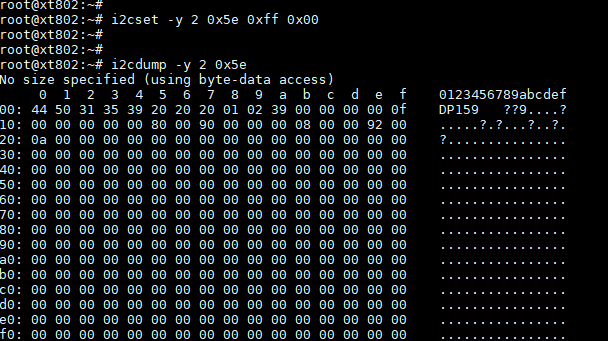

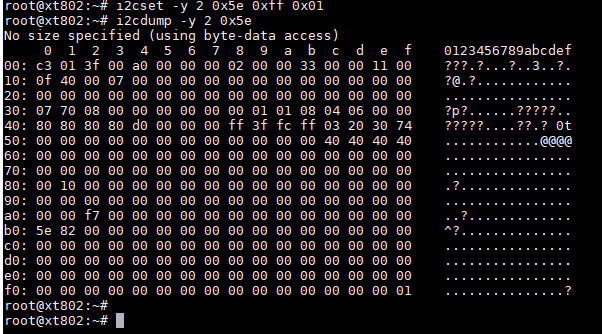

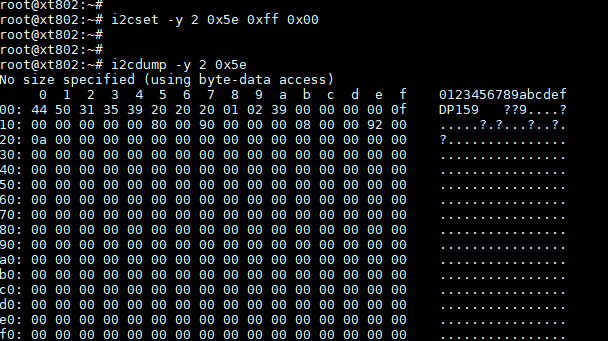

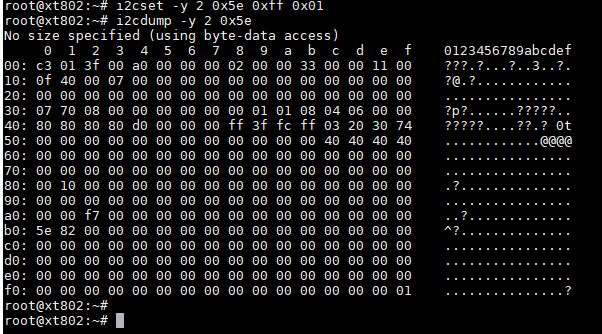

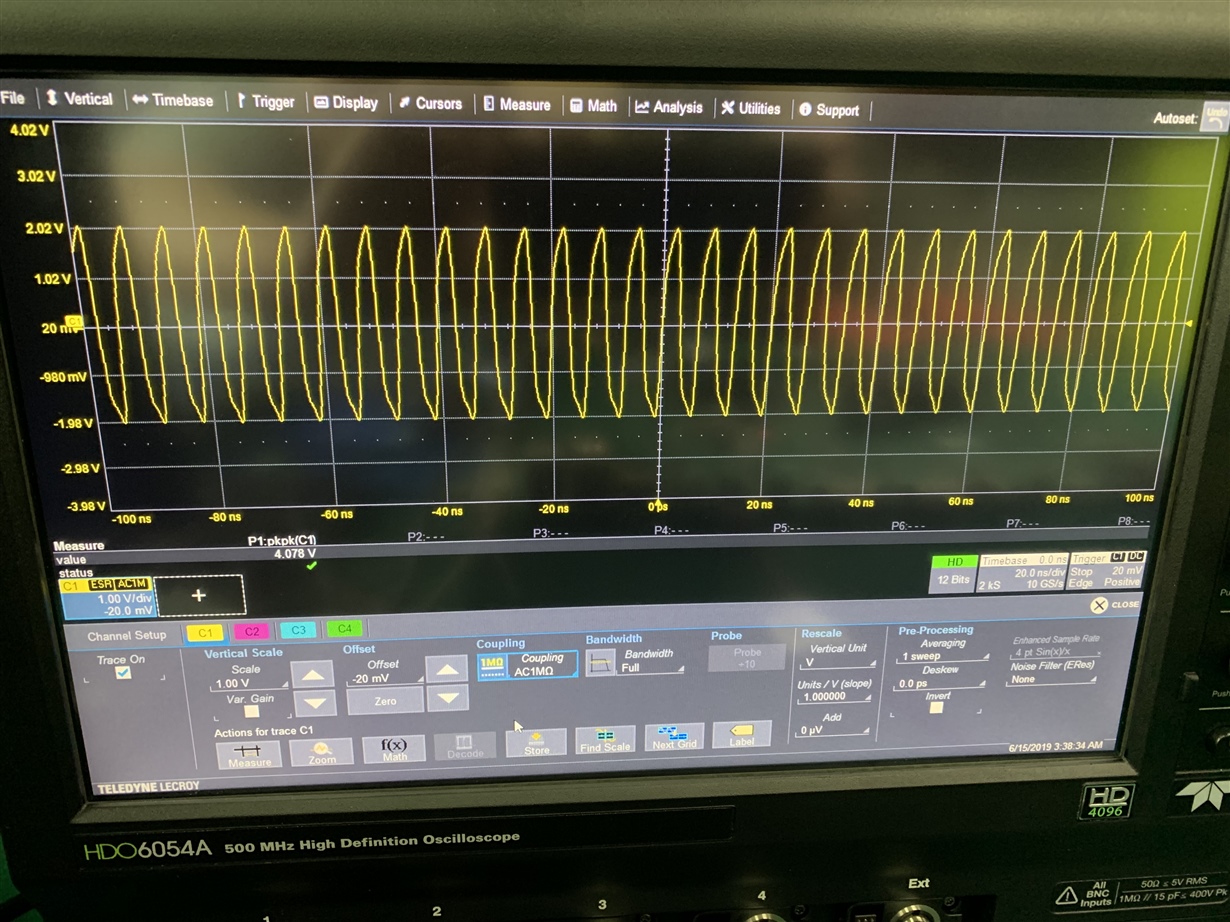

customer is using FPGA output HDMI signal to DP159, then SN159 send to TV, they will find there is sometimes the picture will disappear for around 2~3s, then recover, if they change DP159 to redriver mode, the issue will be solved. what's the possible cause of this issue? The original setting which has issue is as below, they use default setting , and source is not using DDC. tks a lot!