Part Number: TMDS181

Hi Team,

One more question regarding standby mode power consumption of TMDS181.

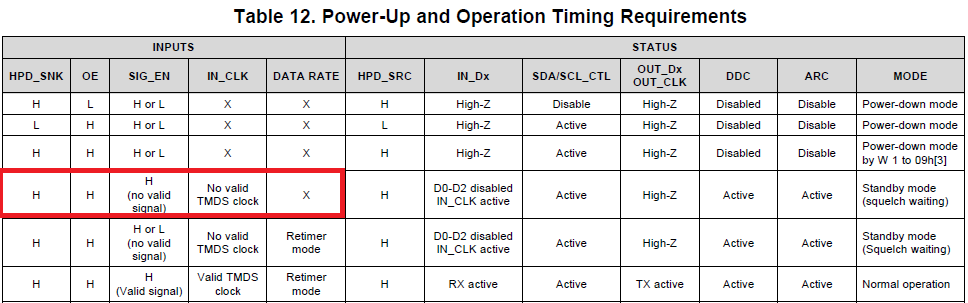

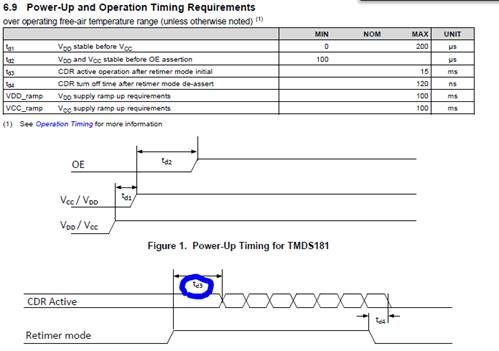

Following below configure of red mark; cusotmer found TMDS181 have 2 kinds power consumption situations.

1. Cable plugged, PC enter “Sleep” or CHROMA pattern not present HDMI signal. I measure consumption current of TMDS181’s 3.3V (include VDD 1.2V)

In this situation, the power consumption will reach 46mA

2. Take of HDMI cable: the power consumption will only 4.7mA

The TMDS181 standby power consumption is too much.

Question:

1. Would you please provide comment on the TMDS181 power consumption spec and how to min the pwoer consumption?

2. please reivew schematic HW setting correct while debugging situation.

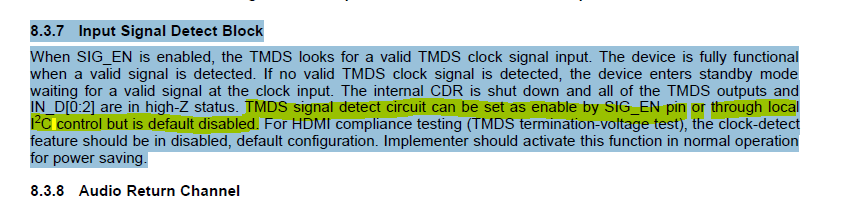

d/s shows that SIG_EN pin can be config by strap pin or I2C.

3. One more question regarding VIH voltage. customer follow TI reference design to use 62Kohm which is near to 65Kohm pull high to 3.3V. customer measure SIG_EN pin voltage, the voltage reduce to 2.5V. could you please provide comment for this?

schematic link

BR,

SHH