Part Number: SN65DP159

Other Parts Discussed in Thread: TMDS181

Dear,

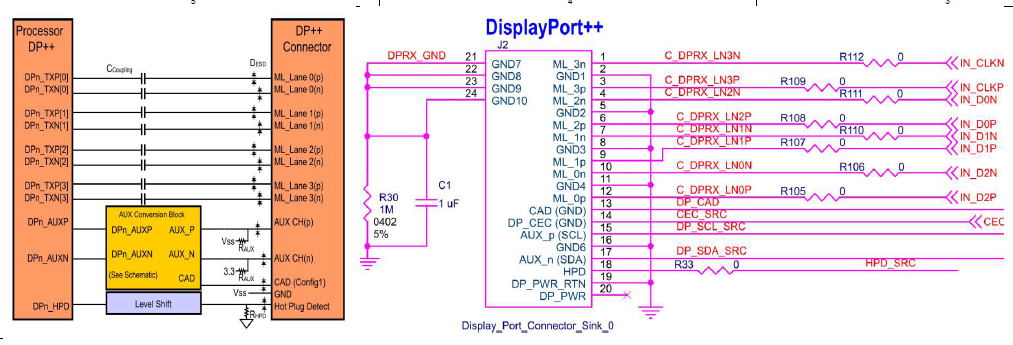

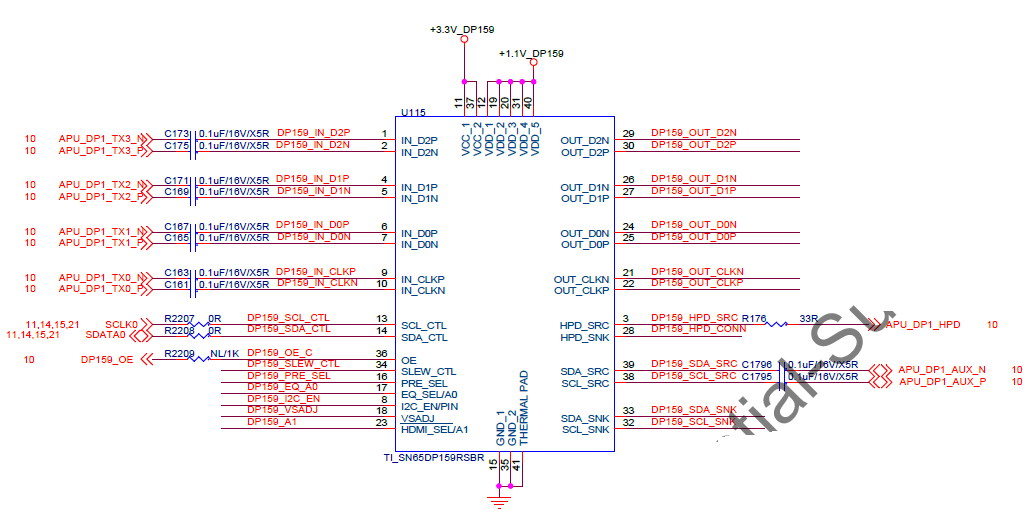

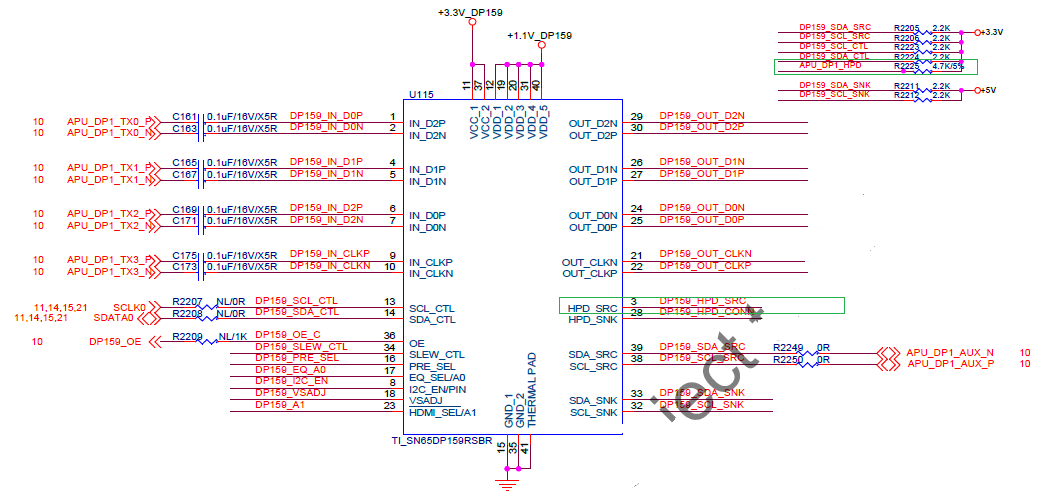

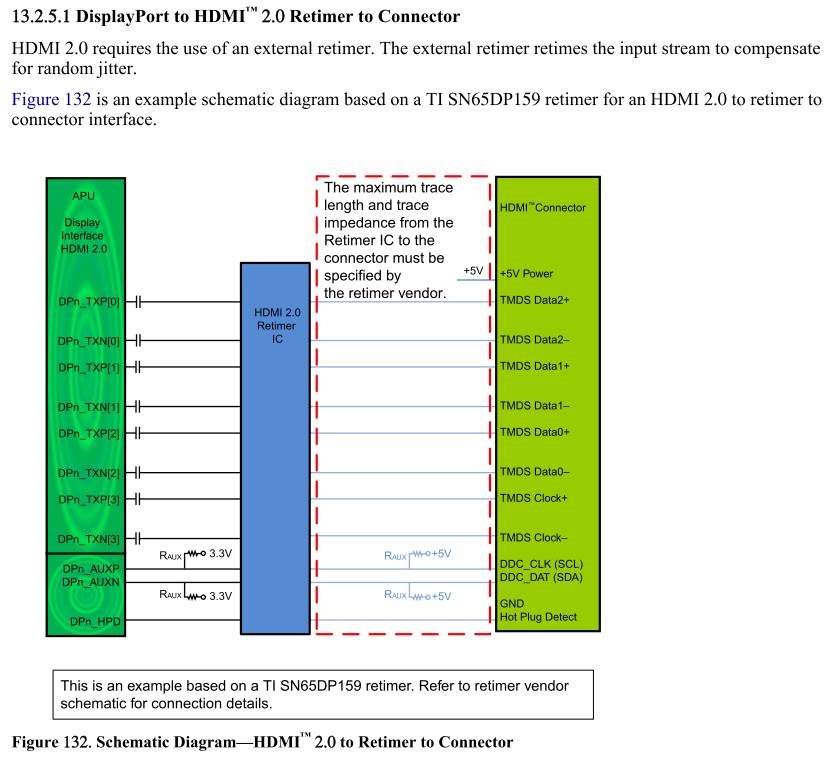

for AMD FP4 Type3 GX-215JJ ,PDG suggestion TI SN65DP159 solution , we need double confirm schematic and some question:

1. SNDP159 was can use HDMI to HDM? in our design is DP to HDMI but some question as below:

2.DP AUX Pin from CPU to SN65DP159 was need series cap?

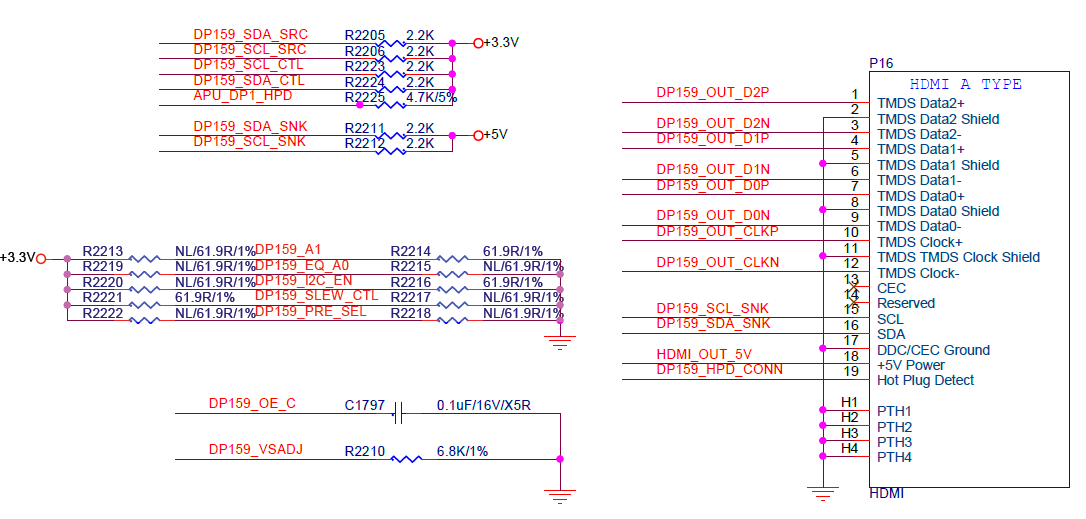

3. about HDMI output, we just reserved chock or need series cap or need add level shift?

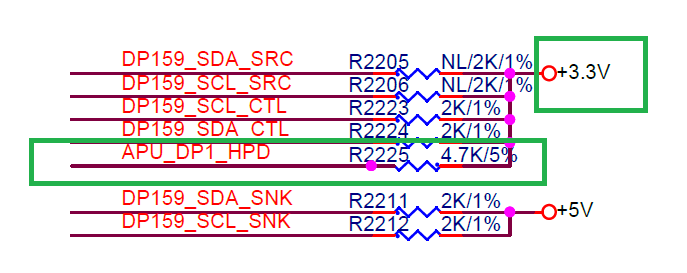

4. I2C Bus address and strap pin we need clarify( EQ_SEL pin was address pin, so need to setting FIXEQ at 7.5db or 14db) how to setting? currently I2C default we setting disable.

below as schematic

2.

3

If any suggestion, Please advise me.

Thanks,

Best regards,

Lawrence.