Hello TI Experts,

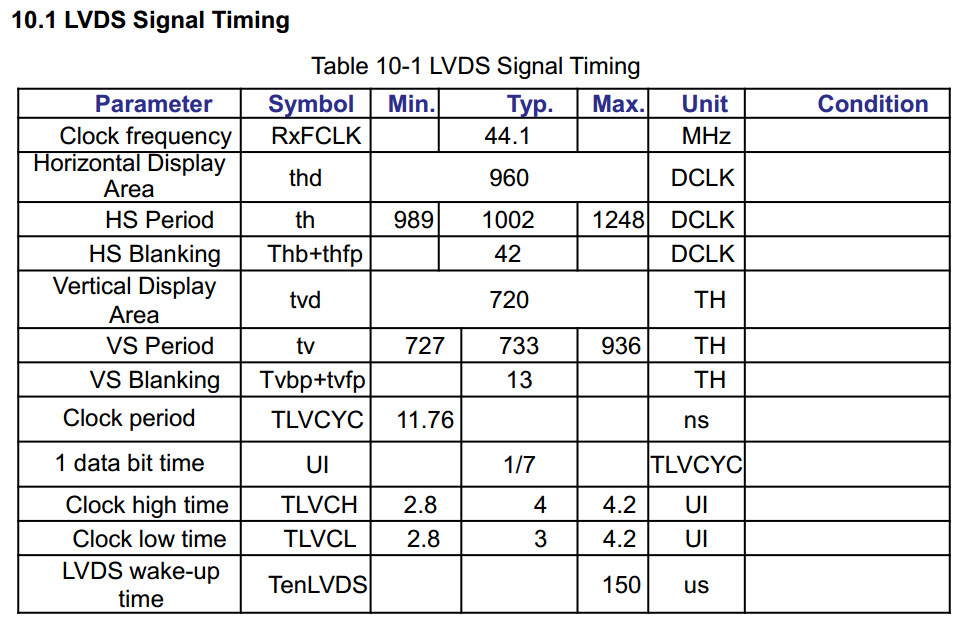

I am now using DS90UB948 with 1920x720 display but the internal test pattern mode doesn't work well,there is LVDS output but CLK is wrong.

***2lane FPD-LinkⅢ Input, Dual Link OpenLDI Output***

The internal reference oscillator(nominally 200MHz) is integer divided ( N=3 ) to generate the target pixel clock . The actual measurement LVDS output CLK is 23Mhz which should be close to 66.6Mhz.

Please help to confirm it.

Thanks.

Best regards.

Ray