Part Number: TUSB7320

Other Parts Discussed in Thread: TUSB7340

Tool/software: Linux

Hi,

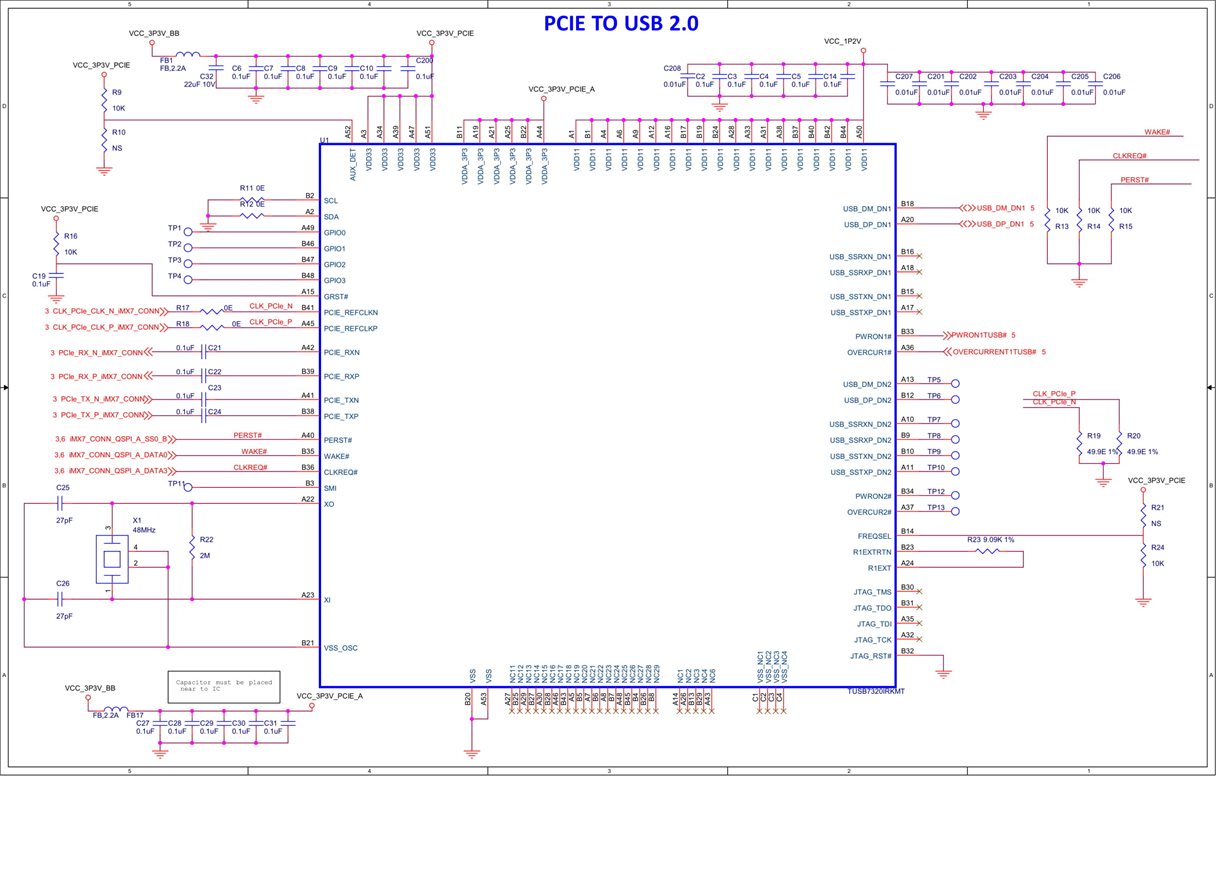

We are using the following design to interface TUSB7320 in our board.

We have ensured that all the power up sequences are followed correctly. Also the 3.3V is enabled after 1.2V. But the WAKE# pin always in HIGH state and we couldn't able to establish PCI link. Are we missing anything in the design? Kindly help us to resolve this issue.

Thanks,

Koil Arul Raj.S