Dear team,

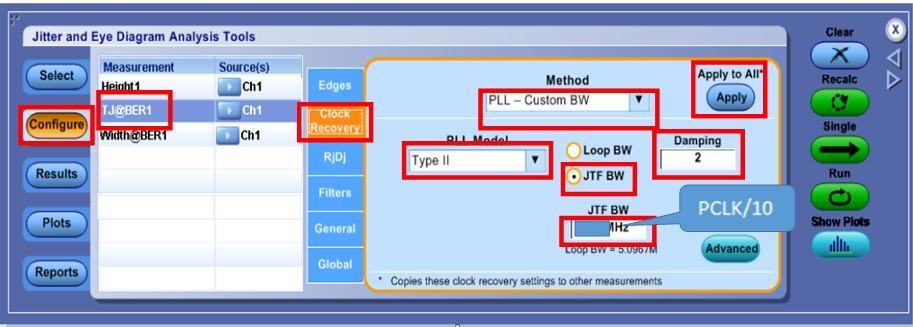

The following oscilloscope tests the eye diagram setting interface, about the PCLK/10 option, and what is the PCLK's frequency?

For example, our application, 949 and 948 pairing, two lane transmission, at HDMI side PCLK is currently set 154MHz, then what about the JTF BW frequency? It should be 154/10 = 15.4MHz, or 154/2/10 = 7.77MHz?

Could you please help answer this question?

Thanks & Best Regards,

Sherry