Part Number: DP83620

Hi Team,

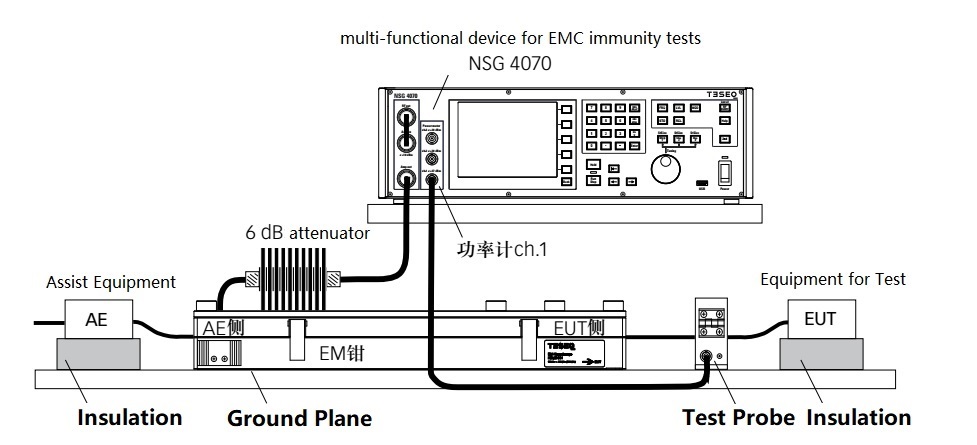

My customer is doing the design with DP83620 with RMII mode. When they do the EMC test with some frequency wave form(RMS=10V) as below: they found that, if the frequency is set to 50Mhz-60MHz, the DP83620’s communication would be lost sporadically. If setting the 51MHz as the test frequency, the dp83620 would always fail with Ethernet communication.

By contrast, they did the same test on two other Ethernet port, one is DM9000, the other is Intel I210. See PCB for the position and layout. But there’s no issue with those two expanded Ethernet ports.

So they’d like to learn whether there are some approach could help to improve the EMC test performance?