Other Parts Discussed in Thread: DS90UB953-Q1, ALP, USB2ANY

Tool/software: Linux

Hi

I am debugging the system of DS90UB954-Q1&DS90UB953-Q1 by the tool ALP.

There are some differential STP wires for test.

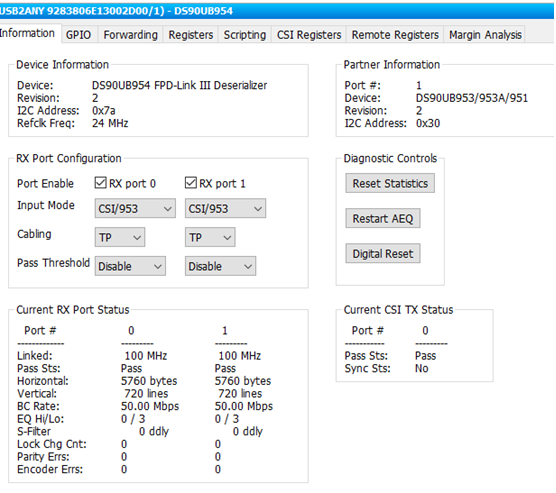

When I used vender1 3.5m wire, it works well above 60 hours at about 25°C and there is no any errors. Picture as below

And the margin analysis of port0/1 as below, it seems well.

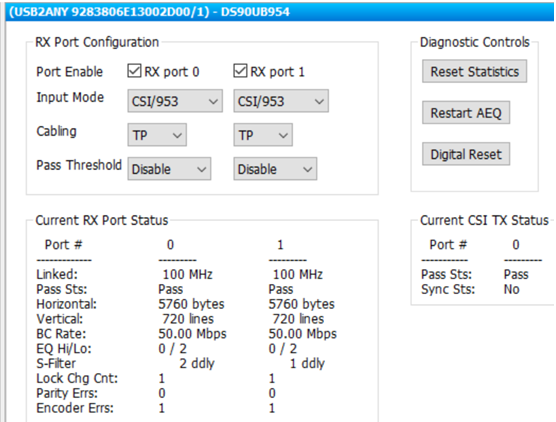

But when I use vendor2 3.5m wire, it run about 12hours at about 25°C,and there are 2 encoder erros of port0 and port1. Picture as below.

The margin test of port0 and port1

Now, I have some questions, thanks for your reply

1. What's the judgement standard of the FPD-Link system?In my opinion, it should be works well from low to high temperature, and should be no link loss and no any errors.

2. The current AEQ setting is default, for the vendor2 3.5m wire, what can i do to optimize the parameter in order to reach the goal of no any errors. But for my question 1, it should also compatible with the other wires, different temperature, and the old age wires.

3. In the ALP "current RX Port Status", what's the meaning of EQ Hi/Lo? This value is unmatch with the register 0xD5. For example, reg 0xD5's value is 0xF2, the Floor_value is 2(reg 0xD2's bit2 is 1), but EQ Hi/Lo is 0/2 or 0/3, it's unmatched.

4. In the ALP "current RX Port Status",What's the meaning of "S-Filter" and "ddy"?

5."Lock chg cnt" means "Lock change counter", is it restart AEQ?

Thanks!