Hi Sirs,

Sorry to bother you.

Could you help double check our schematic as below? Any suggestion are welcome.

Schematic:

Some question need confirm too.

1) I set to use Strap Pin to adjust the setting. Are SCL_CTL / SDA_CTL I2C I/F can be floating? (No Pull up)

2) But I also reserve the possibility to connect the above I2C to PCH I2C to let the BIOS set this HDMI IC. At this time, those Strap pins, for example, can be double-selected by Strap pin or I2C.

For example, how to connect SLEW_CTL Pull up/down

EQ_SEL, HDMI_SEL also set I2C Address, will set the top pull up / down

Other I2C_EN, TX_TERM_CTL has other functions or has the upper piece Pull up/down

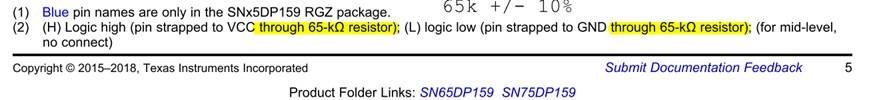

3) Strap pin should use 65K ohm resistor, but this resistor value not in our internal parts pool. So what is the allowable range of resistance values?