Hi Team,

My Customer is using 954&913A. The current situation is as follows:

BC channel can respond normally.

Sensor end has data output.

913 has data input.

Do not know how to test FC signal.

The sensor data is YUV422, using RAW10 high 8 bits.

Register configuration is as follows (Address on the left and register value on the right):

x1 0xff

0x4c 0x1

0x58 0x58

i2cset -f -y ${I2C_BUS_NUM} ${primary_devaddr_7bit} ${SER_ALIAS_ID_ADDR} ${REMOTE_SER_ADDR_8BIT}

i2cset -f -y ${I2C_BUS_NUM} ${primary_devaddr_7bit} ${SLAVE_ID0_ADDR} ${AR0144_ADDR_8BIT}

i2cset -f -y ${I2C_BUS_NUM} ${primary_devaddr_7bit} ${SLAVE_ALIAS_ID0_ADDR} ${AR0144_ADDR_8BIT}

0x6D 0x7F

0x70 0x1E //RAW10 ID

0x71 0x1E //RAW10 ID

0x7C 0x80

0xc 0x1

0x33 0x3

0x20 0x20

0x1F 0x03

Could you help customers check the register configuration?

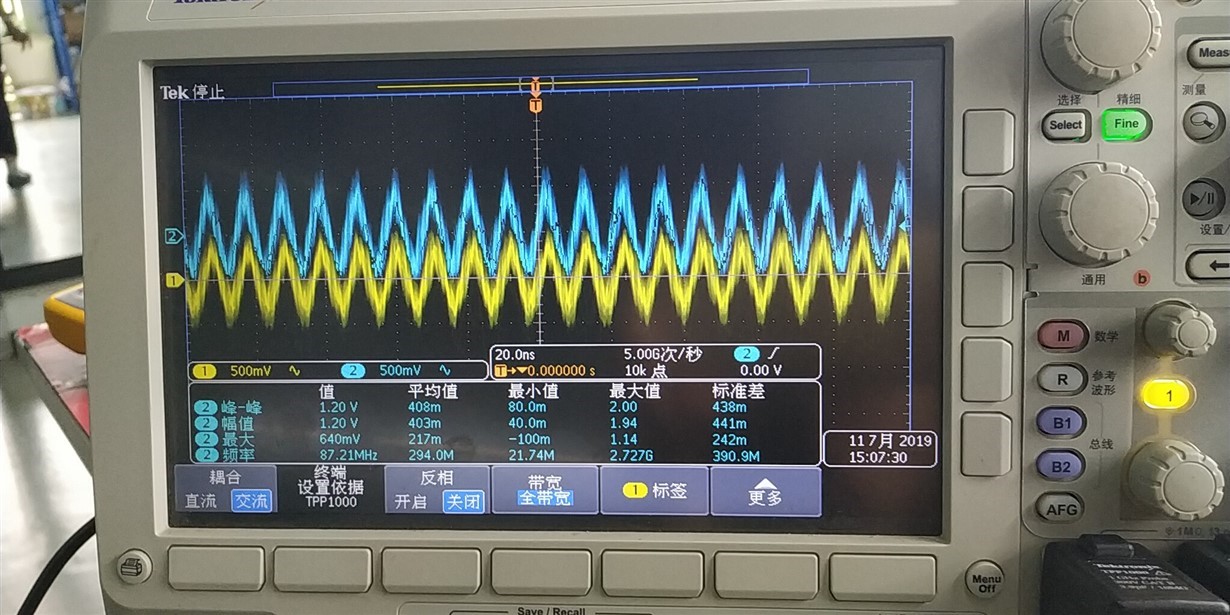

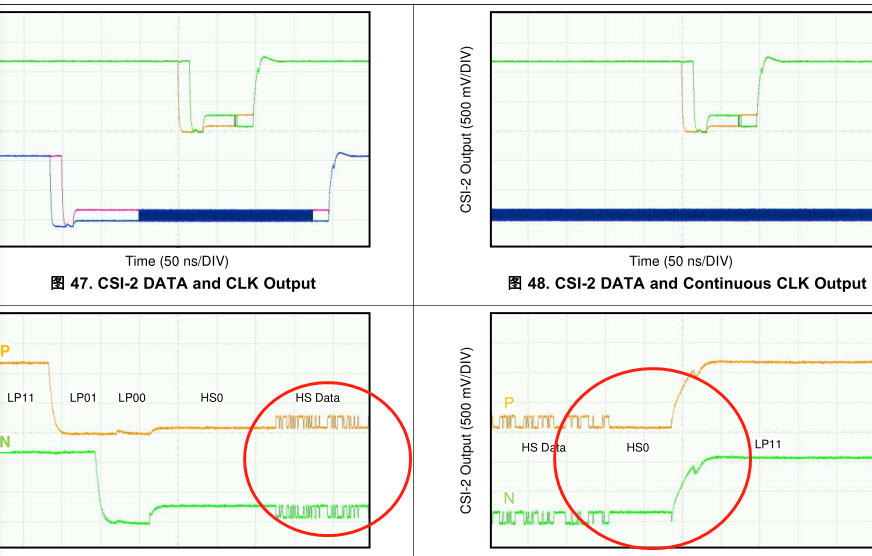

The waveform of CSI output is inconsistent with the datasheet. The measured clock and data waveforms are as follows:

Customers need the following support:

1. Confirm whether there is any problem with the configuration of CSI end and port and whether there is a lack of configuration. If there are any questions, help me point out and revise them.

2. Is the measured waveform normal?