Hi Team,

My customer is using DP83822I as MII mode operation with Register [0X0017] be set as '0049', but when capture the TX_CLK, TX_Dx & RX_CLK, RX_Dx waveform, found a issue that:

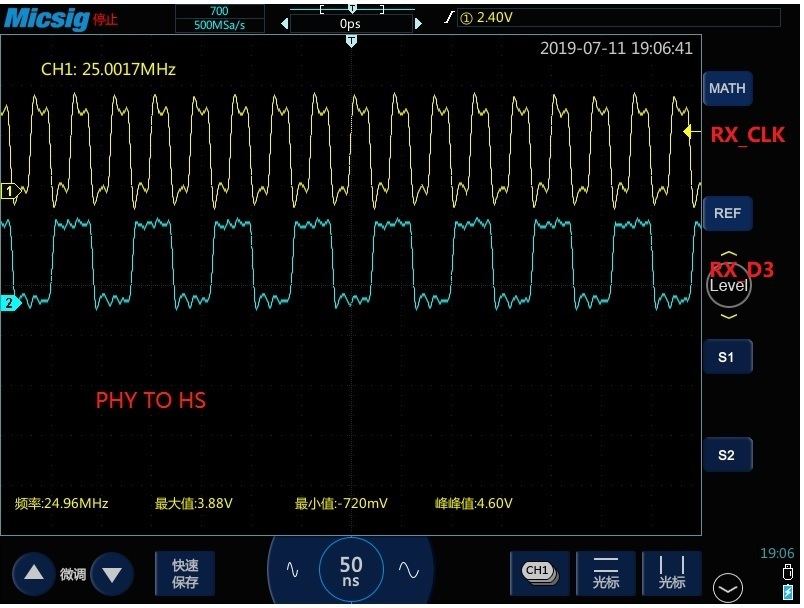

The TX_CLK looks like be interleaved(TX_Dx data be received at the falling edge), and based on such waveform, customer also can capture the data/packet loss at high speed Ethernet communication, detail TX/RX waveform and customer sch as below:

At this moment, Register [0X0010] read back data is: 0715, and when try to write Register [0X0042] to add TX_CLK phase shift, found the value of Reg-[0x0042] always be 0200 and can NOT write successfully.

So need your kindly help to check and comment:

1. For the TX_CLK & TX_Dx waveform it's incorrect right? and if yes what's the potential reason at DP83822 register configuration, HW design, or customer system potential issues?

2. If configure Register [0X0042] is a potential way to fix this issue, could you help to take a look how to configure it successfully?

Thanks & BRs,

Cheney