Tool/software: Code Composer Studio

Dear,

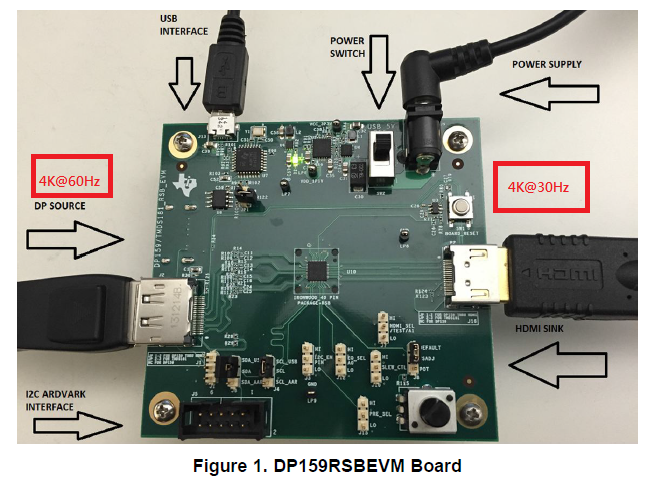

We make sure DP Source was can support 4K@60Hz , but connect DP159RSBEVM and we find HDIM signal only can support 4K@30Hz

How to setting EVM? or this is IC limite condiction, like Displayport Dual-Mode v1.1?

If any suggestion, Please advise me.

Thanks,

Best regards,

Lawrence.