Part Number: SN75DP130

Hi Team,

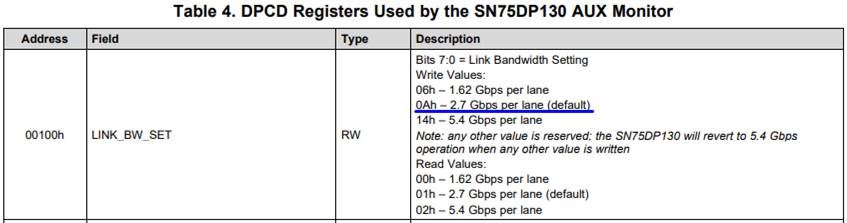

Our DisplayPort (source) using the SN75DP130 with link training returns an HBR (2.7 Gbps/lane) link rate and we are suspecting the redriver LINK_BW_SET default has something to with this.

Our Intel GPU supports HBR2 (5.4 Gbps/lane) so we expect it to use the HBR2 link rate on the DisplayPort with the redriver.

Is there a way we could change the LINK_BW_SET default to 14h – 5.4 Gbps/lane? Or is there a way we could let the redriver choose that bandwidth during link training? (Our sink and cables support HBR2 as well)

Screenshot below is taken from http://www.ti.com/lit/ds/symlink/sn75dp130.pdf p21

Looking forward to your response.

THanks!

Best Regards,

Alfred