Part Number: SN65LV1224B

Other Parts Discussed in Thread: SN65LV1023A, , SCAN921224

Hi,

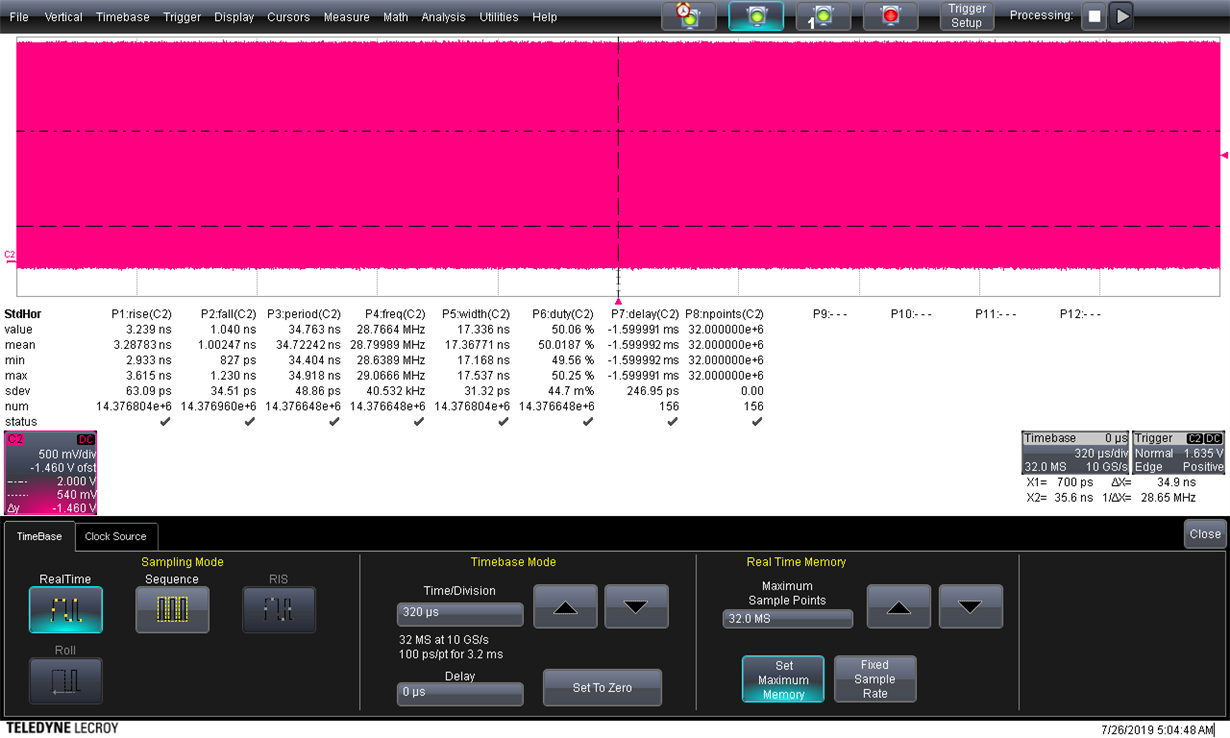

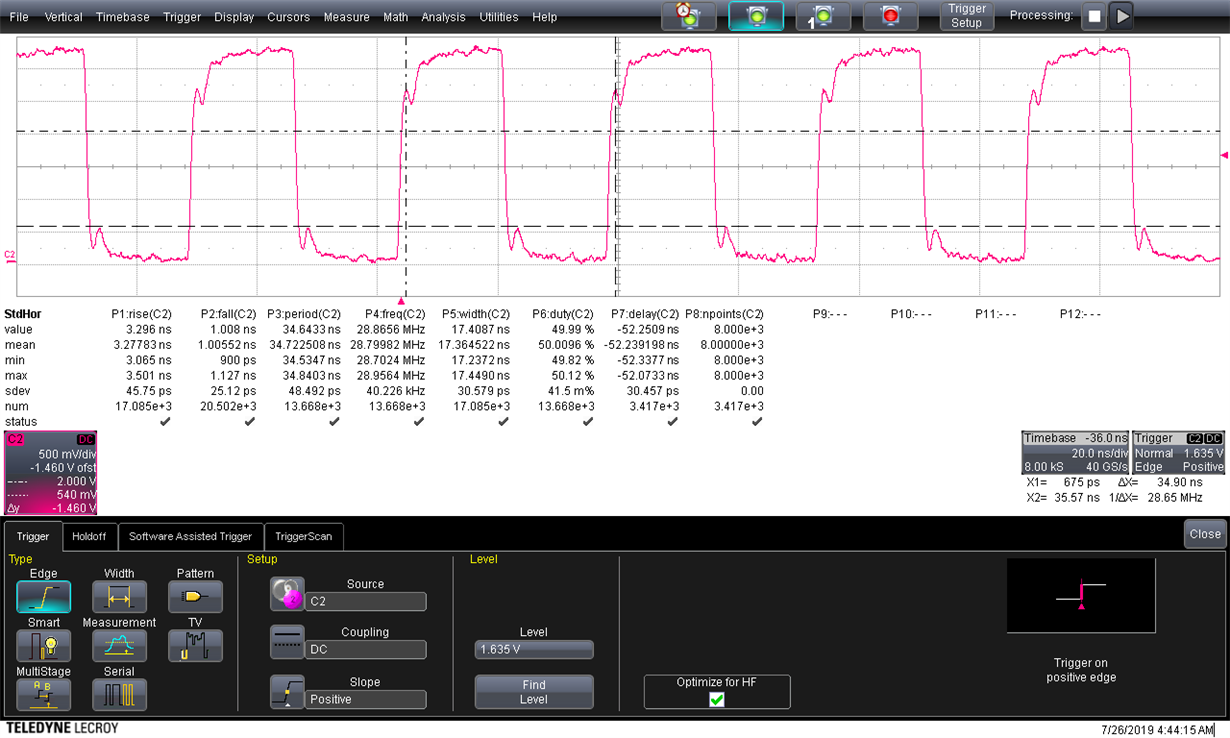

The SN65LV1224B and SN65LV1023A are located on the same PCB and receive their RefClk's from two separate FPGA IO's sourced by a embedded PLL. The frequency is 28M8Hz.

In the connection between both devices is a 33ohm resistor in each signal line at the transmitter side and one 100ohm between the + and - signal lines at the receiver side.

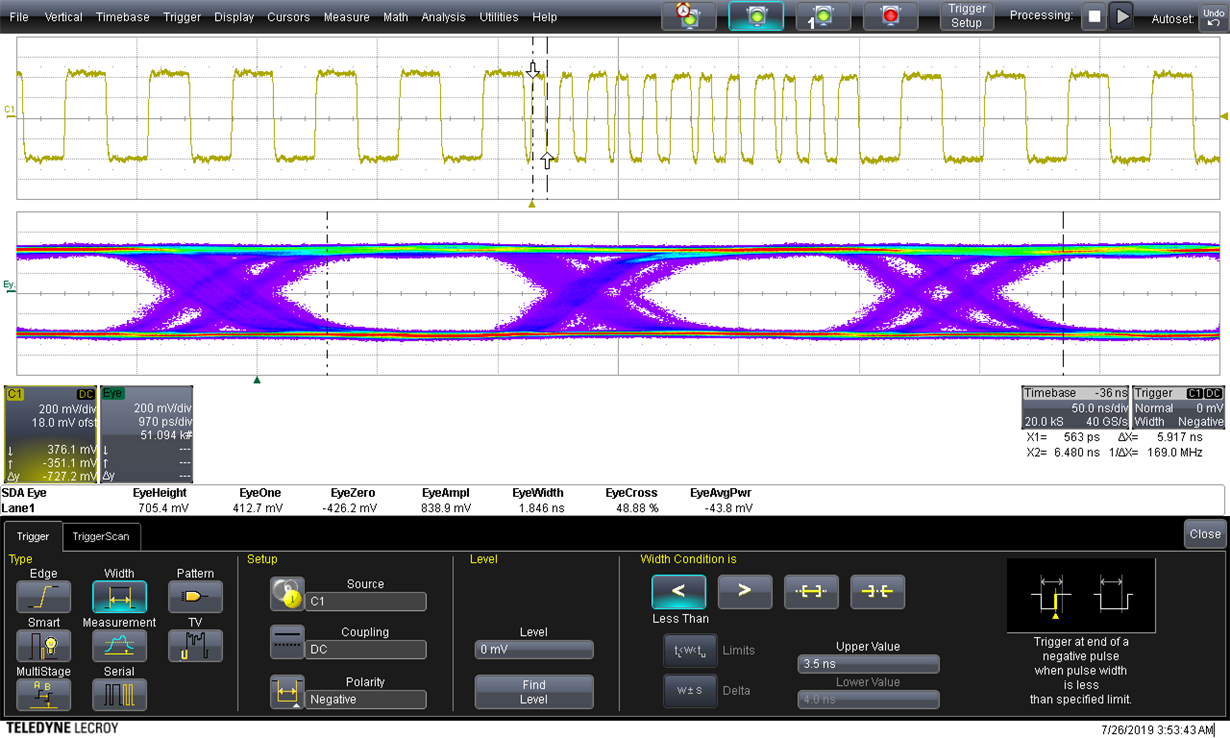

When I use a loop back cable the SN65LV1224B is not able to lock.

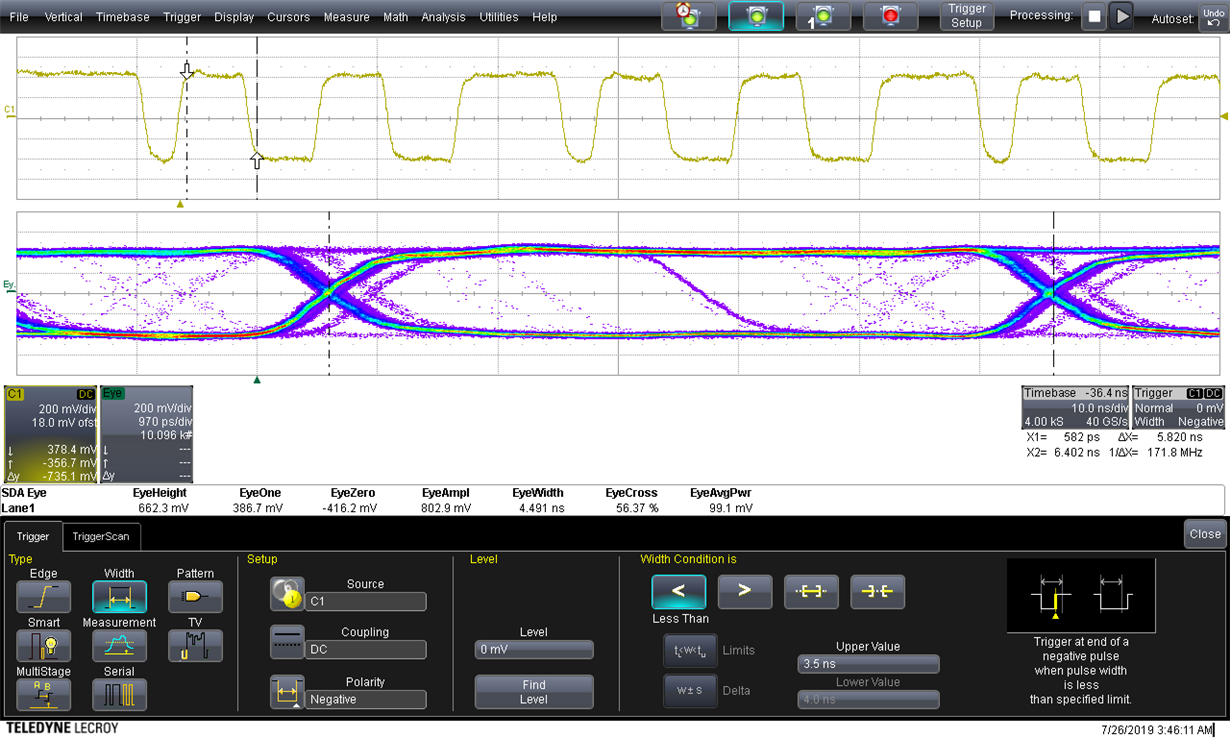

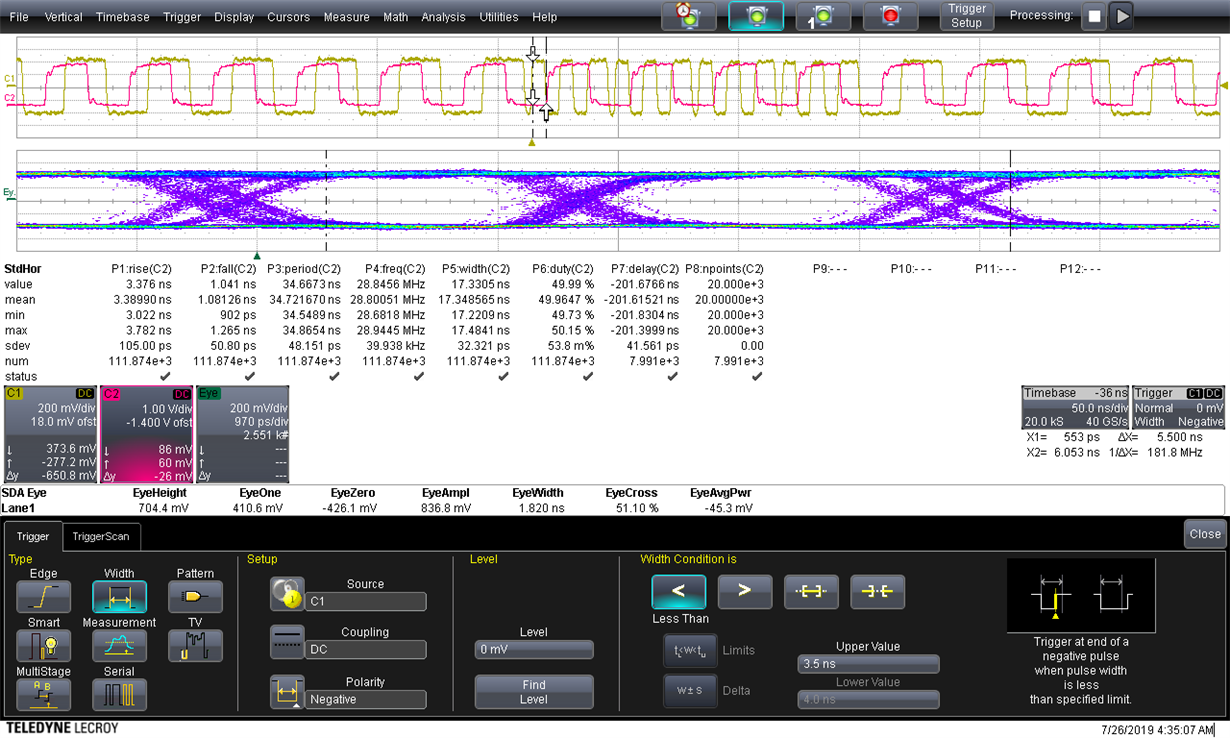

Adding the differential probe (Lecroy WL-PLink + D830 and DXX30-SP) connected to the Teledyne/Lecroy SDA 808Zi-A scope, the SN65LV1224B locks and transmitted data is correct received. Even when the scope is switched OFF but still connected to the mains, the lock remains and received data is equal to the transmitted. When the probe is disconnected from the scope and held to GND of the board everything remains working correct.

What could be the problem?

The reference clocks seem to be OK, because locking is possible.

The transmitted SN65LV1023A data is correct. When connected to a DS92LV1212A, the device locks and passes the data correctly.

On the previous version of the board the serializer: DS92LV1021A and deserializer: DS92LV1212A were used without any problems.

Thx