Other Parts Discussed in Thread: DP83640, DP83TC811

Hi,

We are currently debugging a new design of ours with the DP83TC811R-Q1 PHY.

Our MAC requires it to be strapped to RMII slave mode, and the exact same interface is confirmed to work correctly with both DP83640 and NXP TJA1100.

Other hardware straps are using autonomous mode and 100BASE-T1 Master mode. All straps were verified by reading back the appropriate registers from MDIO.

On the cable side we get a solid link with various other T1 link partners (Marvell, Broadcom, NXP), but the RMII interface is not working as expected. The bus is live but the timing between signals are completely off by several clock cycles. RXDV and RXD0 do not transition high on the same clock cycle, which is expected per the RMII specification.

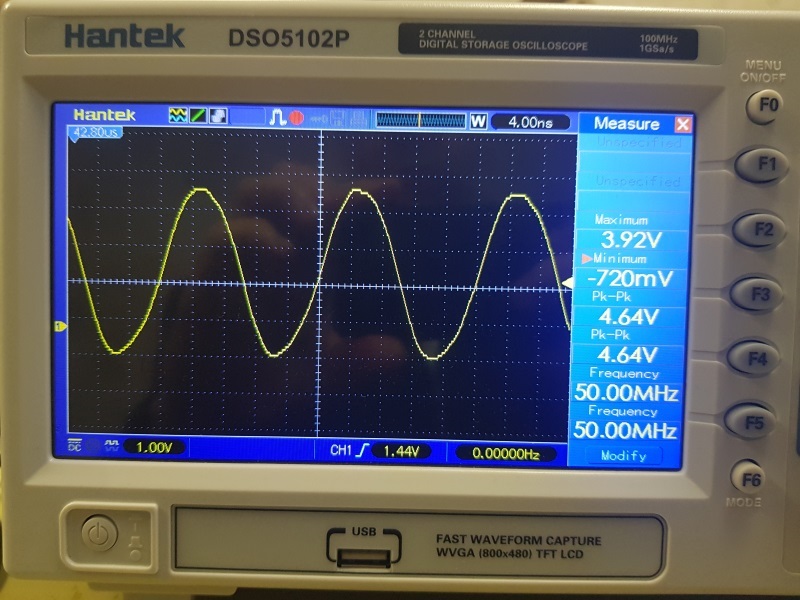

Below is an exaple of expected behavior using a TJA1100 PHY and measuring RXDV (ch1) and RXDO0 (ch2). Both transition high simultaneously as expected.

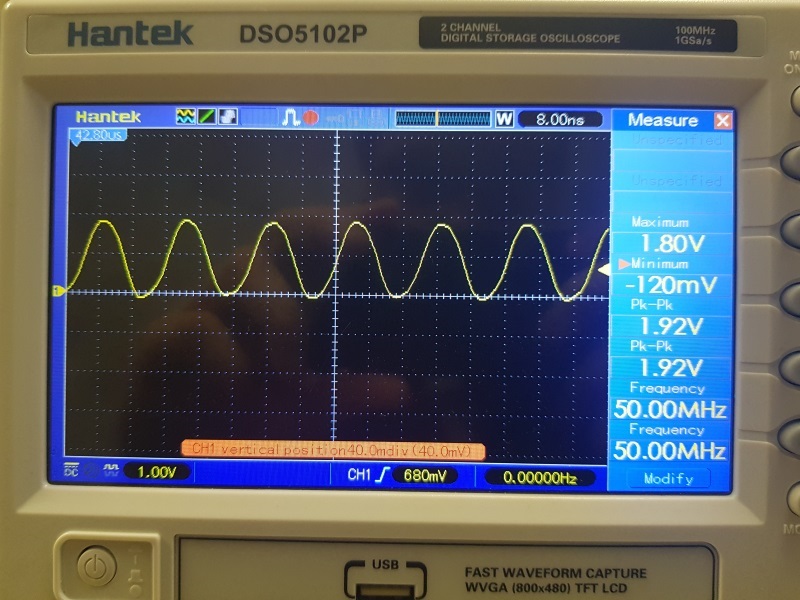

The same measurement is repeated below with the DP83TC811R. RXD0 only goes high about 120ns after RXDV. This delay is also inconsistent and jumps between ≈96ns-134ns.

The same delay is consistent with what we notice on captured packets, where the data bits appear somewhat delayed.

Can you suggest where the problem lies and suggested debugging? Do you have a working design with the PHY strapped to RMII slave mode?

Unfortunately our MAC is fixed to RMII master and cannot be changed to any other mode.

Thank you

Luke