Part Number: DS90CR288A

Hi Team,

I have a confirmation with DS90CR288A.

Customers are evaluating DS90CR288A.

I think that the setup hold time is not kept in the output waveform of CMOS / TTL.

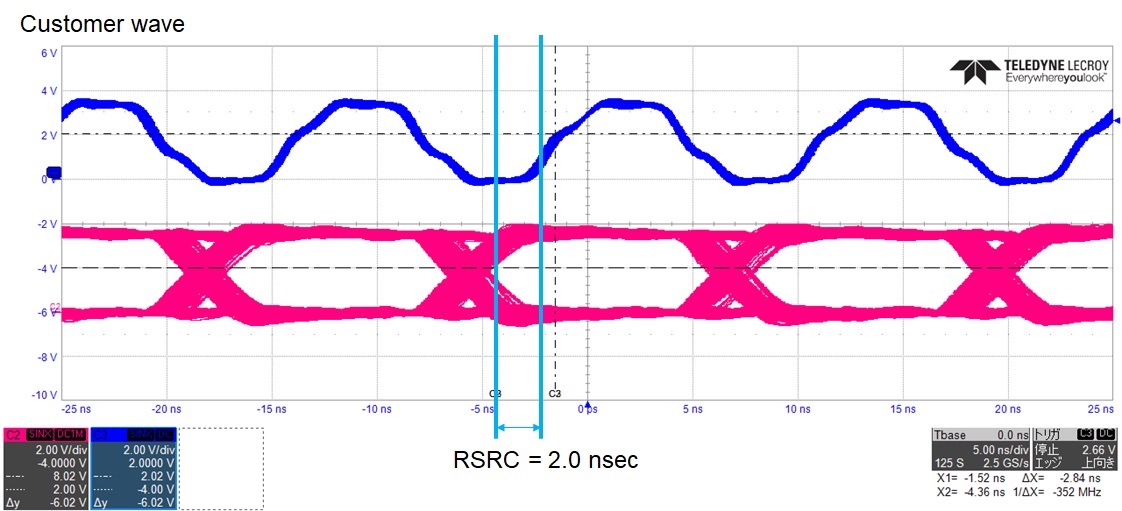

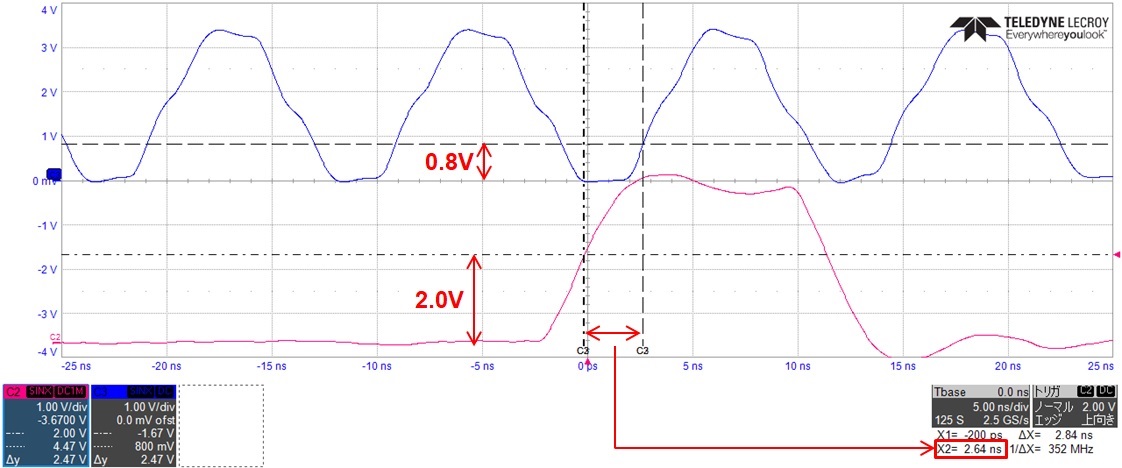

Below is the waveform measured by the customer.

The data sheet spec says 3.5nsec, but it is output below the spec.

Is this spec correct?

I think that the product is not output correctly. What do you think?

Depending on the device, the image may not be displayed correctly.

Best Regards,

Ishiwata