Part Number: SN65HVD72

Other Parts Discussed in Thread: TIDA-01090

Hello TI Team

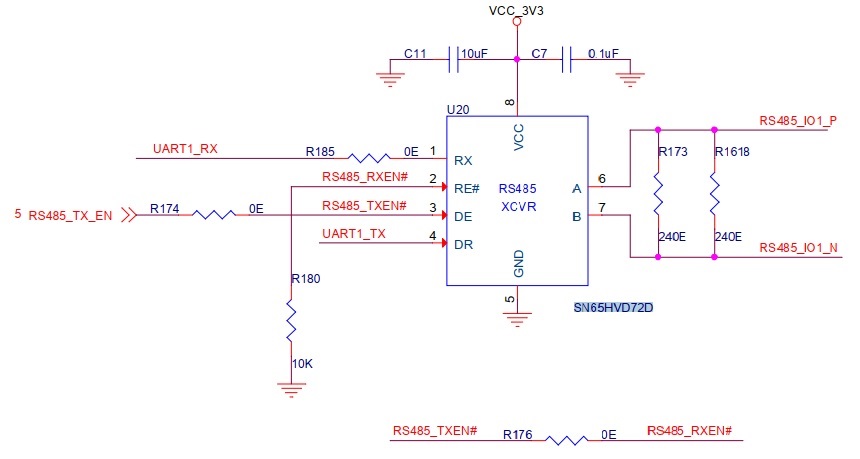

Currently we are using SN65HVD72D chipset, and controlling its DE and RE pin through single GPIO. Have a look at the attachment.

By making GPIO either high/low we are enabling its Driver/receiver manually, its working fine in this condition. Now we want to operate this chipset in auto transreceiver mode as it should work. Please suggest how can we configure this chipset from SW side or we need to do some updation from HW side.