Hello,

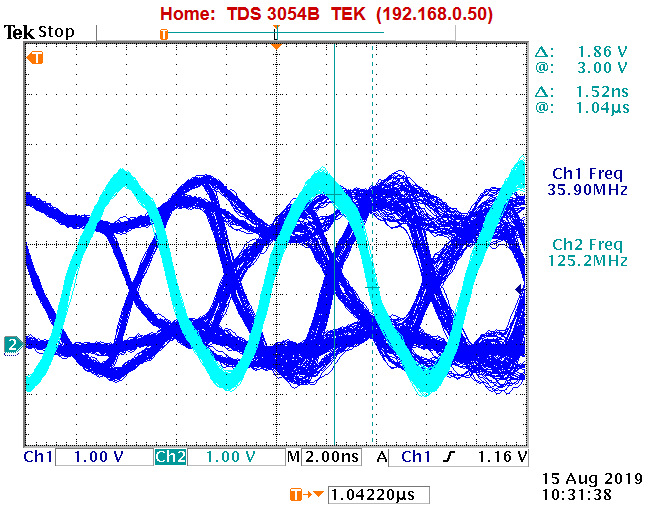

We are experiencing issues communicating through a particular DP83867E phy on our board under thermal stress. This phy reaches a temperature of roughly 70C when we lose communication to the processor it's linked to. We use this phy on several other places on the board that do not lose connection. I have included a page from our schematic as well as screen shots that show the layout from the phy to an ethernet switch. on the board. Also included are 'eye' diagrams of the TX[0] data & clock and the RX[0] data & clock. You will notice that the RX wave forms are much cleaner than the TX. We suspect this might be due to an impedance mismatch (we do not have the 22ohm resistor in line like on the EVM). We'd like help determining what is to blame for the data loss using any tools or procedures you can provide. Some notes on current performance:

- Communication is maintained through thermal stressed, but cannot be re-established

- We use a similar PHY circuits in a couple other places on our boards that will sometimes experience the same issue. However it is usually U102 that exhibits the error

- We do not have controlled impedance on the magnetics side of U102 but we do on the other phys

- The TX clock each might have to be shifted to the right a bit to hit the center of the data 'eye'

Thank you for your help. I am available for any questions.