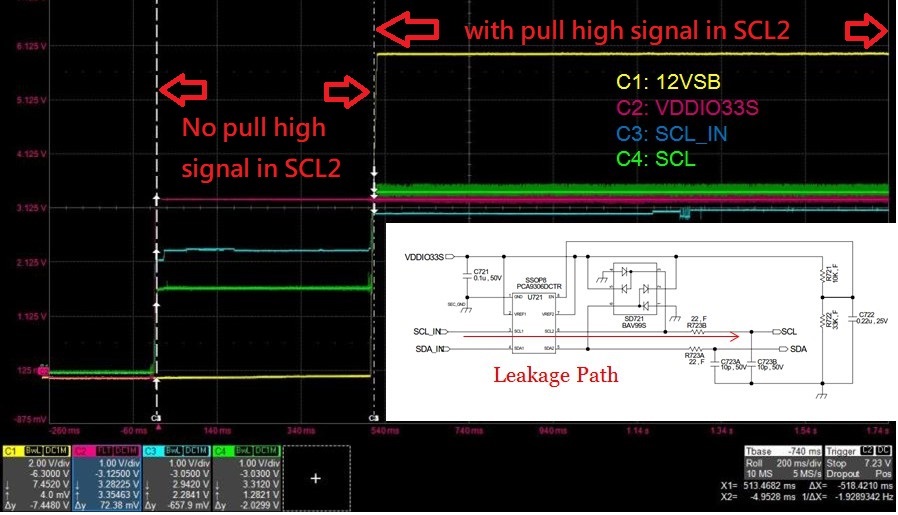

We use the below circuit for the PCA9306 design. We find when the SCL1 provide the signal input, then the output signal just only half of Vref, 1.5V. When we pull high a 3.3V with series 50k resistor at SCL2 bus. Then the SCL2 signal can turn to high as same Vref. May I know the SDA/SCL bus need to pull high voltage or not? Why?

BR,

Gary