Hello,

The following phenomenon has occurred in my customer.

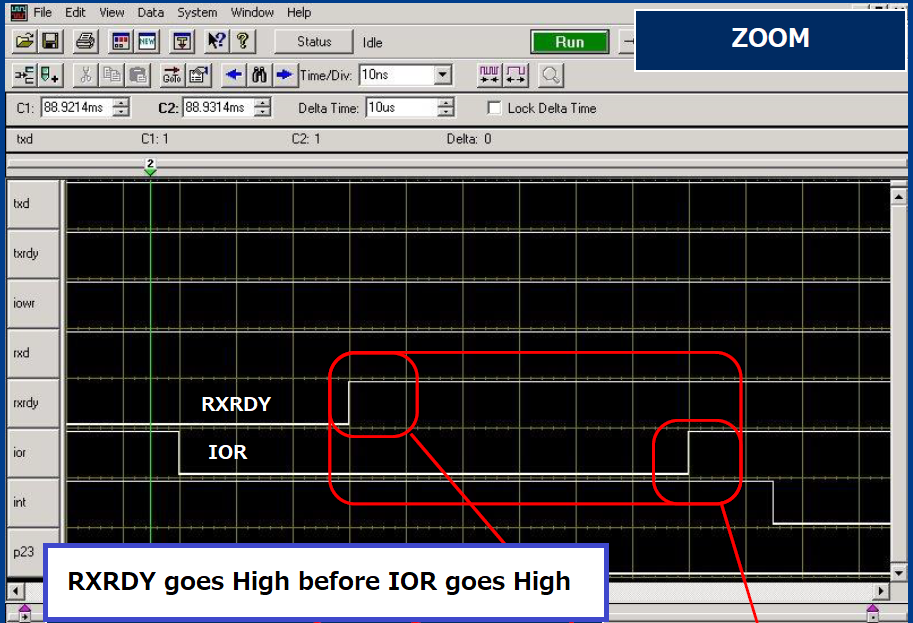

RXRDY goes High before IOR goes High in Receive Timing in FIFO mode.

It looks different from D / S Figure 6, why? Is this correct behavior?

I'm aware of this phenomenon as follows. Is my understanding correct?

・ IOR Storb width is Characterized only for the minimum value

・ The condition that RXRDY goes High is when FIFO becomes Empty.

・ Even if Low is input to IOR, RXRDY goes High if the Storb width spec is satisfied and the FIFO is empty.

So, I think that is normal behavior.

Is my understanding correct?

Please leave a comment.

Best Regards,

Kaede Kudo