Hello,

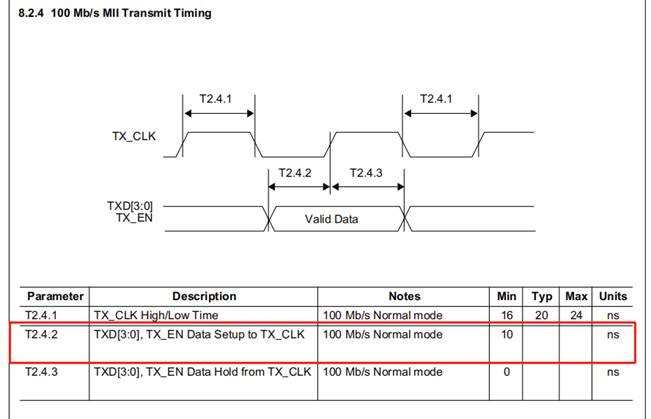

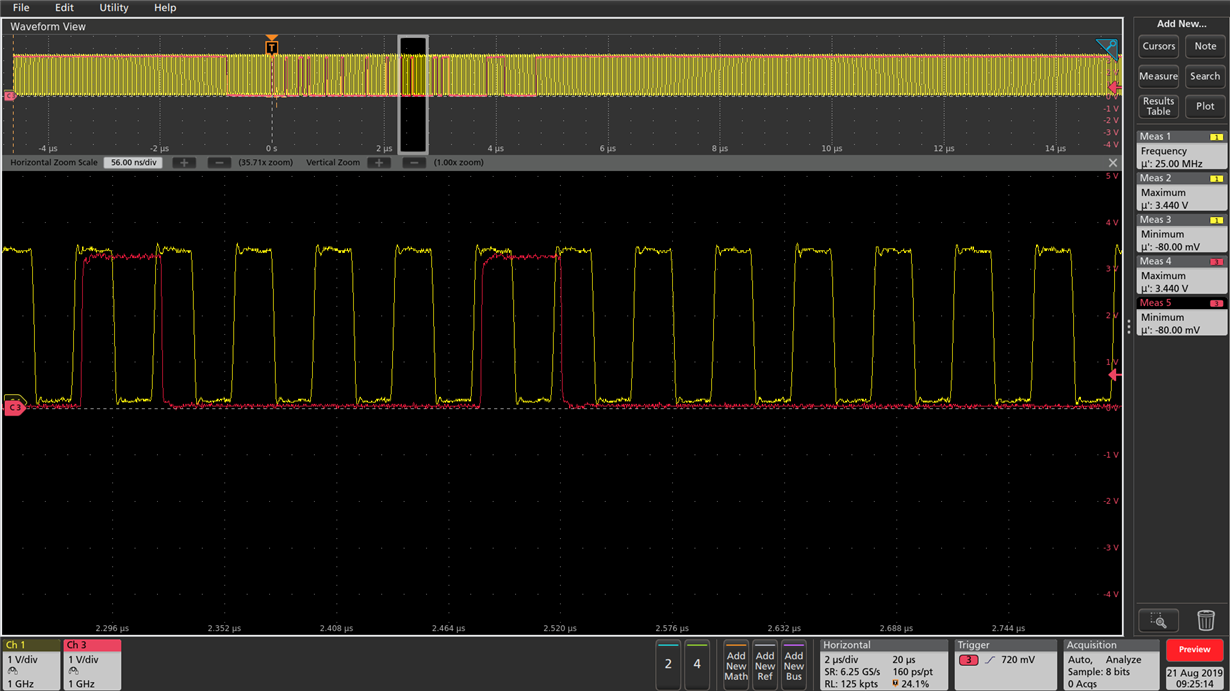

When we recently tested the timing specifications of the MII interface, we found that the MII Transmit Timing of the DP83848N has an index requirement that the TXD setup time is greater than 10 ns. However, the IEEE Std 802.3-2005 standard only defines the TX characteristics of the MAC, and requires the TXD output delay to be 0-25 ns. The CPU (MAC) we use also conforms to this standard. However, the 10 ns requirement of the DP83848N cannot be met when the waveform setup time indicator is tested on the DP83848 N terminal.

I would like to ask:

1. Does the 10 ns minimum requirement of the DP83848N specification deviate from the standard?

2. How should we test the DP83848N setup time indicator?