Hi, team,

I am working on 960+913*4 fpdlink iii cameras. I can use Nvidia Xavier capture frames with 960 + one 913 camera. But when i try 2 913 cameras +960, i can not capture, and mipi wave looks failed.

Here is my config code

ds90ub960_write_reg(client, 0x01, 0x02); //reset

msleep(100);

ds90ub960_write_reg(client, 0x01, 0x00); //reset end

for (i = 0; i < 2; i++)

{

ds90ub960_write_reg(client, 0x4c, (0x01 << i) + 0x10 * i); // RX_PORT0

ds90ub960_write_reg(client, 0x70, 0x1e); // RAW10_datatype_yuv422b8_VC0

ds90ub960_write_reg(client, 0x58, 0x58); // enable pass throu

ds90ub960_write_reg(client, 0x5c, 0xb0); //serlizer I2c addr

ds90ub960_write_reg(client, 0x5d, 0x90); //isp ap0101 I2c addr

ds90ub960_write_reg(client, 0x65, 0x90); //isp ap0101 I2c addr alias

ds90ub960_write_reg(client, 0x6d, 0x7f); //RAW10 mode

ds90ub960_write_reg(client, 0x7c, 0xE3); //FV LV

ds90ub960_write_reg(client, 0x20, 0xF0 ^ (0x10 << i)); //FWD enable

}

ds90ub960_write_reg(client, 0xbc, 0xe1); // FV min time

ds90ub960_write_reg(client, 0x6E, 0x10); //GPIO0->GPIO0 GPIO1->GPIO1

ds90ub960_write_reg(client, 0x6F, 0x32); //GPIO2->GPIO2 GPIO3->GPIO3

ds90ub960_write_reg(client, 0x34, 0x00); //csi ctl

ds90ub960_write_reg(client, 0x32, 0x01); // CSI0 select

ds90ub960_write_reg(client, 0x33, 0x01); // CSI_EN & CSI0 4L

ds90ub960_write_reg(client, 0x4C, 0x00); //i2c disable

Here are 960's registers

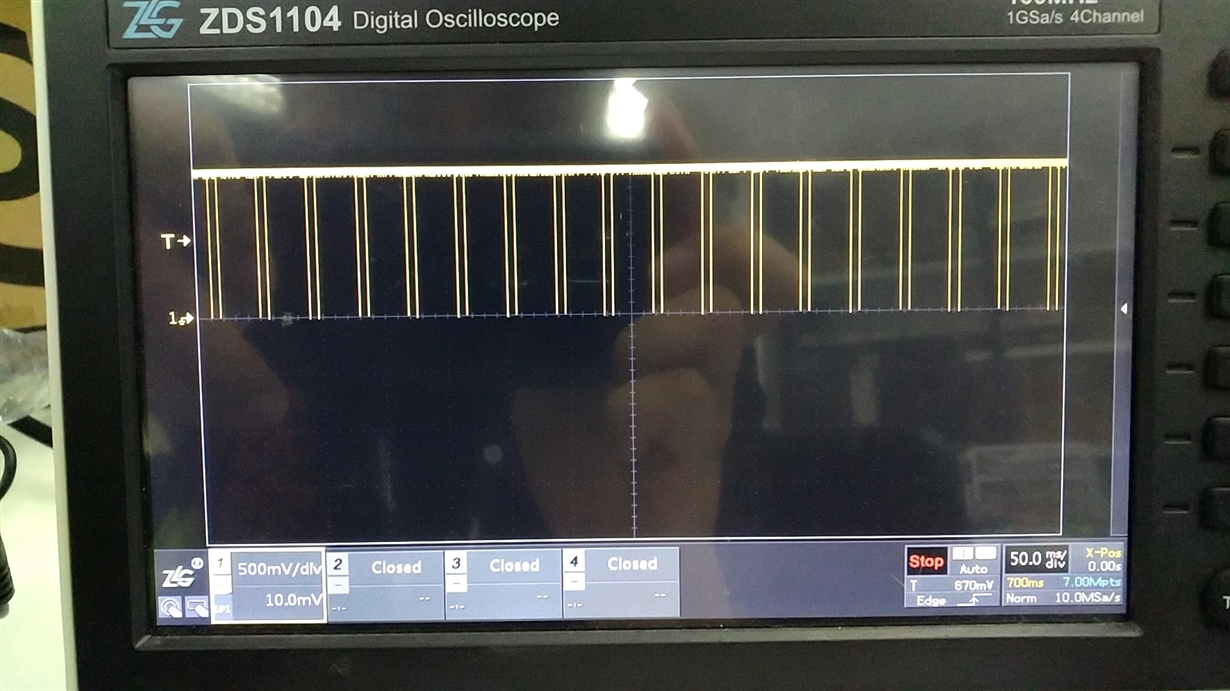

Here is 960 mipi wave