Part Number: DP83867IR

Hello,

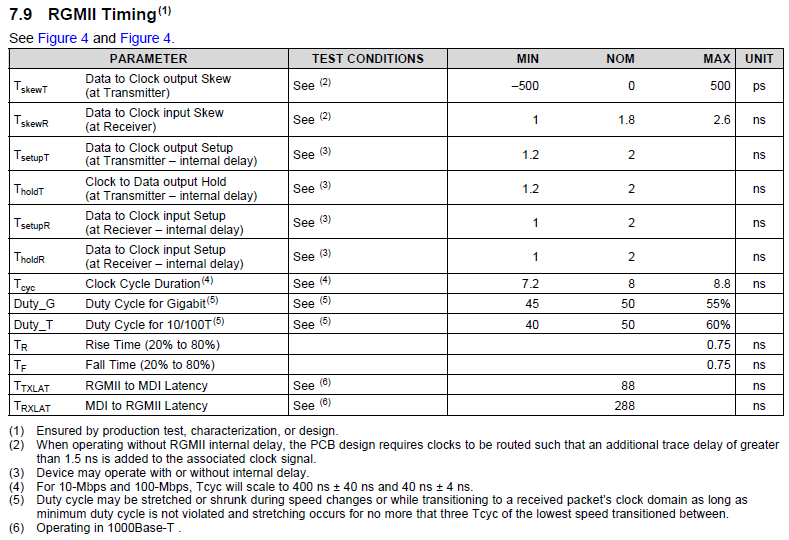

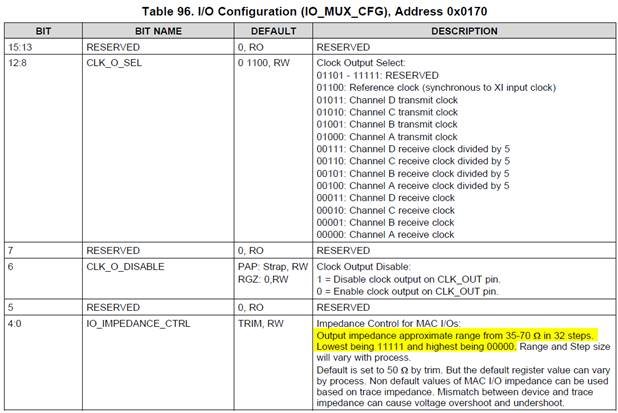

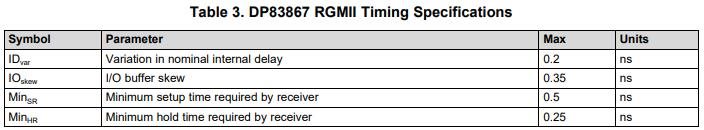

my customer is currently doing a design with the DP83867IR and he has a couple of open questions regarding the RGMII Timing diagrams and figures below:

Why are two different values for transmitters / receivers given here?

Who is the transmitter or receiver? (the customer would have assumed that one of them would have to be their FPGA, but then the question arises as to why TI assumes a timing for the routing path between the transmitter / receiver, but that can not be known at all).

The engineer has currently configured the PHY to internally delay the clock on the Rx side. On the Tx side, the delay is ensured by the FPGA (no delay in the PHY).

Which Setup / Hold values for the Rx signals directly at the output of the PHY can he expect? Which setup / hold values does he have to guarantee at the PHY input for the TX values?

regards,

Stani