Hi Sirs,

Sorry to bother you.

Currently, there is a problem with the debug DS90UB941AS-Q1, the deserializer ID can be read, but the FPD link cannot be locked, probably in the DSI input section.

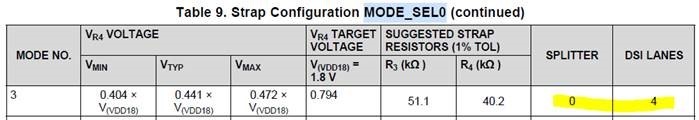

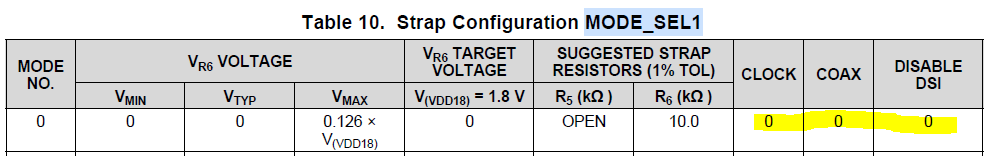

LCD resolution is 1024 x 600. single DSI. STP cable.

Is there a sample code of DS90UB941AS-Q1 initial and HW setting recommendations for reference?

In addition, in the DSI Indirect Register, what settings need to be made in addition to TSKIP_CNT?