Dear team,

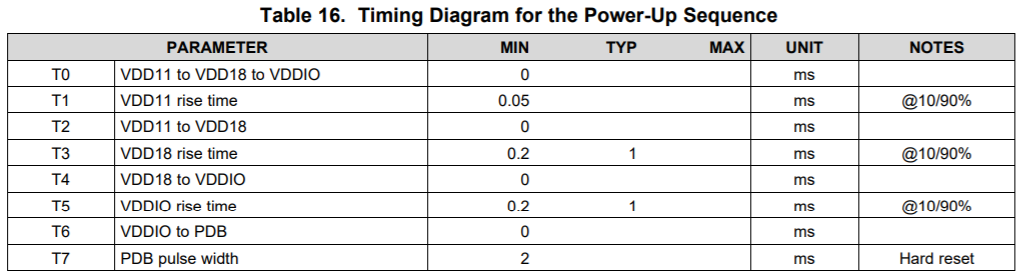

1. The minimum rise time is 0.2ms as below, but the customer's design only has 0.15ms. What is the bad influence?

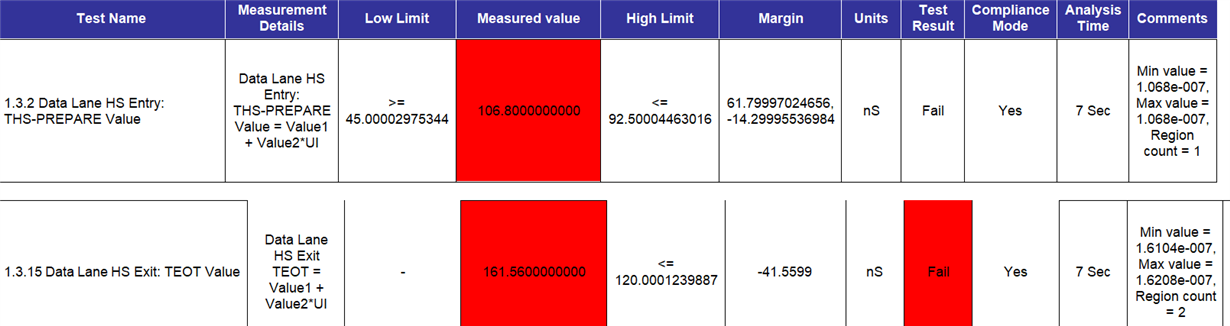

2. below is the customer's MIPI test report, there are two items failed. Do you have any suggestion to reduce these two parameters?

Thanks & Best Regards,

Sherry