Part Number: SN65DP159

Dear all,

I would like to ask 2 questions about operation timing.

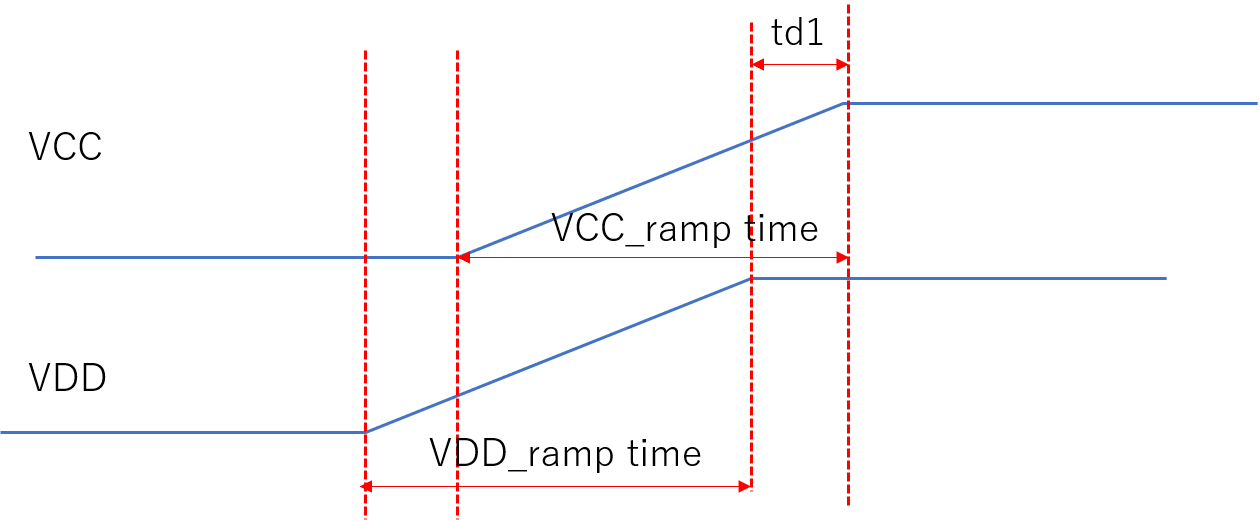

The contents written as meaning at td1 in the table below are “VDD / VCC stable before VCC / VDD”.

What does "stable" as used here mean in the state of VCC or VDD?

(For example, when the voltage has risen to 90% of VCC or VDD, or when VCC or VDD has risen and stabilized)

Also, in the above table, can td1 and VDD_ramp (VCC_ramp) parameters be considered to indicate the part in the figure below?

Best Regards,

Y.Ottey