Hello,

I've tried the board with the Auto-Enable board and I'm receiving signals correctly to the oscilloscope. When I try to force the board to work at 100Mbs the Rx stops receiving but the Tx keeps working.

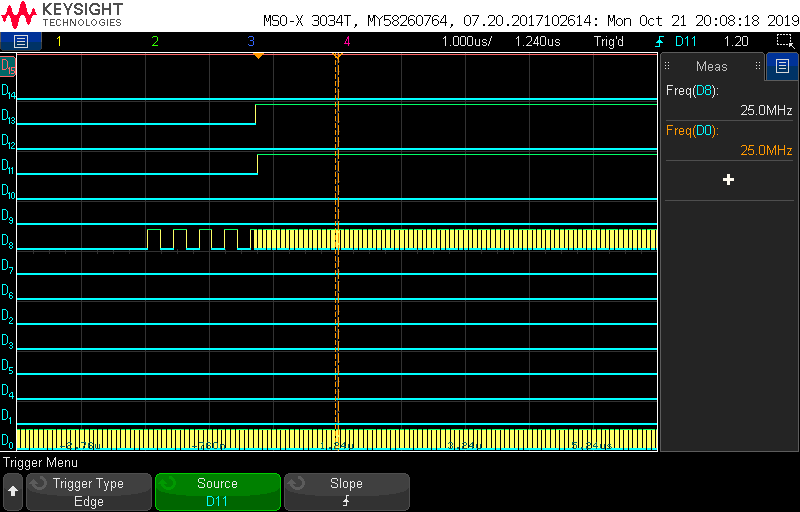

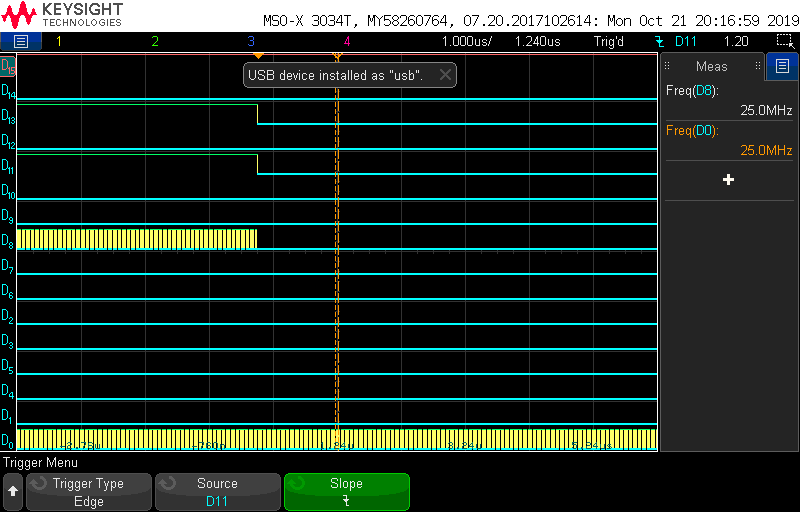

In the Rx side the clock is at 25MHz, the enable is always off, and two data signals are always on. Setting the trigger at one of the data signals I can see that in some moment of time the clock stops working and then it resets to 2.5MHz and after 4 cycles to 25MHz again.

To force 100Mbs i've changed the following register using MDI:

0x0000 0x2100

I've also tried to force link changing the following:

0x0010 0xD448

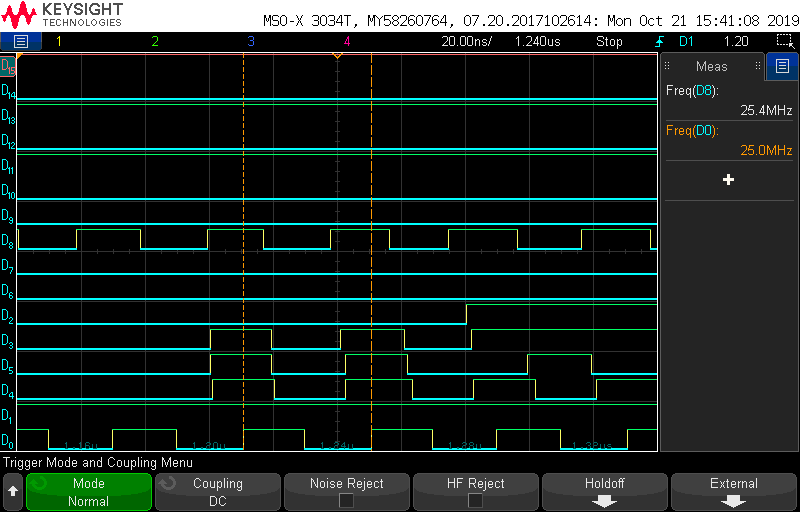

The Tx side works properly but the signals are not correctly aligned between them, but that would be probably a problem of overshooting/undershooting or maybe noise, I will check with a non-digital probe later on, but first I'm trying to solve the problem with the Rx side.

I will attach three images, two of the Rx clock turning off and then on, and the final one of the Tx side. For Rx: D8 is RXCLK, D9 is RX_CTL and D10:D13 are RXD. For Tx: D0 is TXCLK, D1 is TX_CTL and D4:D2 are TXD.

Thanks you.