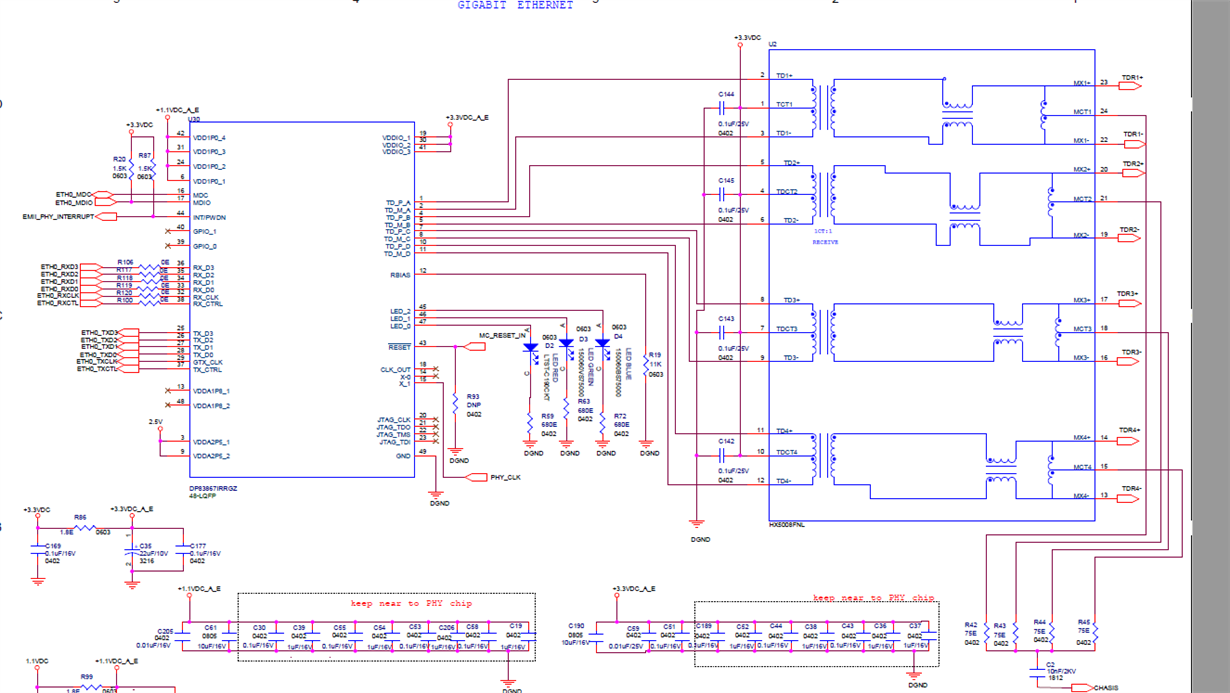

Part Number: DP83867IR

Hello,

i'm using DP83867IR in RGMII mode based on the link phy is detecting the speed but from the Emac RX_CLK is different from that of the evolution board. i'm using analog devices based SHARC development baord(SC589-ezkit) based on that i have designed the custom hardware i can able to check the rx clk on Analog devices board rx clock for gigabit operation it is 125MHZ with 700mVp-p but with my custom hardware amplitude has been reduced to 250mVp-p but still im getting 125MHz wht might be the issue please check the attached schematics Please as per recommendations i have removed 3.3V from the magnetics but still i have not updated schematics assume that magnetics is unconnected to any supply.