Other Parts Discussed in Thread: DP83867IRPAP-EVM

Hi,

When DP83867CRRGZ is released from reset, the target voltage value of the bootstrap pin (RX_D2) cannot be maintained.

We confirmed improvement of phenomenon by lengthening rise time of reset signal.

VDDIO is 1.8V.

RX_D[3:0] in MAC device are input with PullUp resistor. But MAC is not affected by the reset.

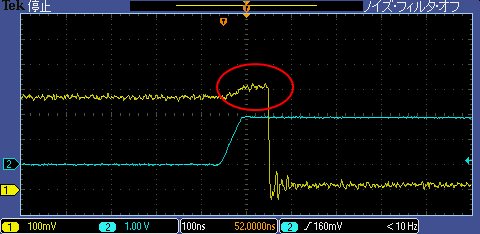

I attached the observed signal waveform.Wave.pdf

It seems that the voltage level of the RX_D2 pin is affected by the reset signal.Moreover, although the terminals such as RX_D0 and LED2 can recognize the set value normally, the voltage level gradually rises after reset.

Please reply these questions:

[Questions]

1) As with RX_D0 and LED2, the level of the strap pin rises after resetting. Is there a path that affects the voltage level inside the IC?

2) RX_D2 has a level fluctuation that seems to be affected by the reset signal, but is there a path that is affected by the reset signal?

3) The phenomenon is improved by providing a slope to the reset signal, but is there a restriction on the rise time of the reset signal?

Best regards,

Kenshow